Mike_Z

Veteran Member

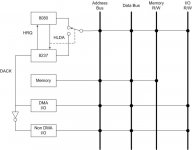

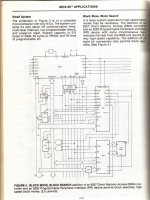

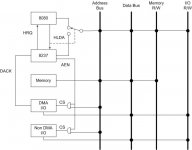

Don't worry about being puzzled, I'm often puzzled and I made the thing. By behind the buffers, do you mean between the 8080 and address buffers? If the 8237 was there, the 8237 address lines would be cut off from memory also. This way the buffers are driving everything on the address bus so the 8080 doesn't have to. I have the MCS-80 manual and my circuit is similar except the address buffers are between the 8080 and the "T" in the address lines to the 8237 (8257 in the picture). I suppose it's all in what you are used to. Seems the simple controllers that I made many years ago were all 8085's yet the prototyping was done on this 8080A and this is all that I have left.

Mike

Mike