Marty

Veteran Member

Hi All;

Dave, once I put it on the BreadBoard, it seems to work exactly as You have described..

"" L9 pin 5 (/PRESET) low for one clock cycle when you press the LDIR pushbutton. It should then remain high. Pin 2 (J) should remain low throughout. Pin 3 (K) should remain high until CP7 goes low - whereupon it should also go low. Pin 6 (Q) should be low until pin 5 (/PRESET) goes low - whereupon it should go high. Pin 6 (Q) should remain high until the next clock cycle after pin 3 (/K) has gone low at CP7 time - whereupon it should go low. ""

So, maybe things are not a Bad as I had previously thought and/or I mis-intrepreted what I thought I saw or it was late Saturaday Afternoon.. Or all of the above..

I am going to while I am at it put the other half of L9 with Leds for the same reason.. It will be easier for me to see, what's going on..

That's done, I was going to take a picture, but my phone/camera Battery got Low, it wasn't plugged in well enough, so it has to charge, before I can take a picture..

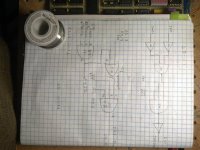

I made another change to the Board, that You can see from the pictures, I made all of the A0-9 and F0-10 signals go to Leds, instead of just what is used, this way if something changes, I don't have to guess, if it's one not connected..

"" You should be able to repeat the above tests with the manual pushbuttons LDMA, LDM, LDMB, LDPC, LDIR (already done), LDAC, EX and DEP.

The results obtained should be the same (the EXEC flip-flop should flip, you should get a series of CPx 'pulses' from 0 to 7, and the EXEC flip-flop should flip back after CP7).

Also note that during this test yo should not see any outputs from J6 (F0..F10) or J5 (A0..A10) (i.e. all of the outputs should remain at '1').

Don't forget to keep checking L10 pin 7 (it should always be '1'). ""

I have monitored L10 pin 7, with my Test Led..

And EVERYTHING Else is fine, and I tested/tried all of the Buttons..

THANK YOU Marty

Dave, once I put it on the BreadBoard, it seems to work exactly as You have described..

"" L9 pin 5 (/PRESET) low for one clock cycle when you press the LDIR pushbutton. It should then remain high. Pin 2 (J) should remain low throughout. Pin 3 (K) should remain high until CP7 goes low - whereupon it should also go low. Pin 6 (Q) should be low until pin 5 (/PRESET) goes low - whereupon it should go high. Pin 6 (Q) should remain high until the next clock cycle after pin 3 (/K) has gone low at CP7 time - whereupon it should go low. ""

So, maybe things are not a Bad as I had previously thought and/or I mis-intrepreted what I thought I saw or it was late Saturaday Afternoon.. Or all of the above..

I am going to while I am at it put the other half of L9 with Leds for the same reason.. It will be easier for me to see, what's going on..

That's done, I was going to take a picture, but my phone/camera Battery got Low, it wasn't plugged in well enough, so it has to charge, before I can take a picture..

I made another change to the Board, that You can see from the pictures, I made all of the A0-9 and F0-10 signals go to Leds, instead of just what is used, this way if something changes, I don't have to guess, if it's one not connected..

"" You should be able to repeat the above tests with the manual pushbuttons LDMA, LDM, LDMB, LDPC, LDIR (already done), LDAC, EX and DEP.

The results obtained should be the same (the EXEC flip-flop should flip, you should get a series of CPx 'pulses' from 0 to 7, and the EXEC flip-flop should flip back after CP7).

Also note that during this test yo should not see any outputs from J6 (F0..F10) or J5 (A0..A10) (i.e. all of the outputs should remain at '1').

Don't forget to keep checking L10 pin 7 (it should always be '1'). ""

I have monitored L10 pin 7, with my Test Led..

And EVERYTHING Else is fine, and I tested/tried all of the Buttons..

THANK YOU Marty

Last edited: