Hi All;

Dave, Thank You for the Encouragement and for the Next Experiment..

I think the way I have it set up is DIFFERENT than what You are currently having me do and check..

But, I will set up the Led's to make sure which one of us is correct OR if neither of us is correct.. As far as what it is doing..

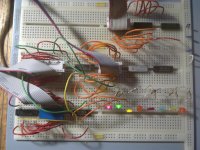

"" As you like experimenting to get things working can I suggest attaching LED's to the following points - L10 pin 2 (schematic LD9), G6 pin 11 and G7 pin 4 (both on schematic LD14). Attach the LEDs so that ON means logical '1' and OFF means logical '0'.

Set the clock speed to very sloooow and wait until L10 pin 2 changes from '0' to '1 (LED OFF to ON). On the next transition of the 'master clock', G6 pin 11 should transition from '0' to '1' (LED OFF to ON) and then (on the next transition of the 'master clock') G7 pin 4 should transition from '0' to '1' (LED OFF to ON). At this point, L10 pin 2 should also transition from '1' to '0' (LED ON to OFF). ""

I think what I have now is Master Clock will turn on L10 pin 2, On the next transition of the 'master clock', G6 pin 11 should transition from '0' to '1' (LED OFF to ON) AND G7 pin 4 should transition from '1' to '0' (LED ON to OFF).

At this point, L10 pin 2 should also transition from '1' to '0' (LED ON to OFF).

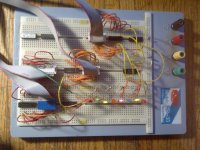

But, Let me set it up for sure and I will Let You know for sure..

I might have some of the sequence wrong as far as who is on and who is off, BUT, I am sure about the second half , that is G6 pin 11 and G7 pin 4..

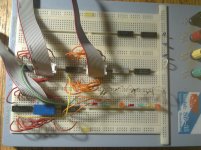

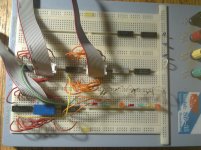

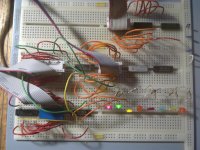

Here is Actually what I have at the present time.. !!!!!!!!!!!!!!!!!!!!

What I have now is Master Clock will turn on L10 pin 2, On the next transition of the 'master clock', G7 pin 4 transitions from '0' to '1' (LED OFF to ON) AND a moment later G6 pin 11 transitions from '1' to '0' (LED ON to OFF), But, before the Master Clock L10 pin 2 transitions from '1' to '0'..

At this point, L10 pin 2 transitions from '1' to '0' (LED ON to OFF).

If I UnderStand What You Want, We do Not have a three Phase Clock, we have a two Phase Clock..

"" Set the clock speed to very sloooow and wait until L10 pin 2 changes from '0' to '1 (LED OFF to ON).

Phase ONE..

On the next transition of the 'master clock', G6 pin 11 should transition from '0' to '1' (LED OFF to ON)

Phase TWO..

and then (on the next transition of the 'master clock') G7 pin 4 should transition from '0' to '1' (LED OFF to ON).

Phase THREE..

At this point, L10 pin 2 should also transition from '1' to '0' (LED ON to OFF). ""

Back to Phase ONE..

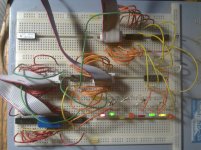

To do this We would need to ADD another half of a 7474 between the two that are Already there..

Which I could do, on the BreadBoard..

I Already have L10 and G6 and G7 out on the BreadBoard, So all I need to do is Bring out the 7474 and then I can see about making things like Your Description..

I am going to 'Fix' Phase One and Phase Three, so they match Your Description, But, for Now only on G6 pin 11 and G7 pin 4, then I will add Phase Two, so to speak..

THANK YOU Marty