Christoffer

Experienced Member

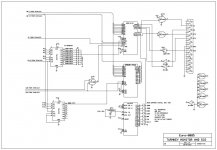

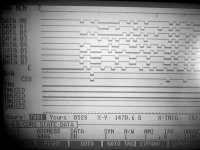

Now that I've done some more testing (and gotten it hooked up to a proper terminal) I'm looking into the slow transmission issue. If I type fast I can also get it to mess up receiving, but I don't know what'd cause an ACIA to run fine, but very slow. The baudrate gen. must be fine, since it transmits the characters correctly.

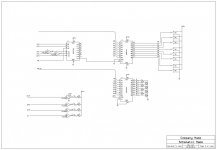

I'm still suspecting the E line, since that's the main enable for the chip, and is used to clock everything in it, it seems from the datasheet. using a 3x faster crystal, it should be clocked a lot more frequently, thus cycle the ACIA more often, but I'm not sure that's the right thing to look at for a problem.

It could be a timing issue with the E clocking. Perhaps inserting some equal amount of spare NAND gates as a delay would do some good.

If we assume it's a software thing (when I force-outputted, no delay), it must run in the check transmit data register empty loop. Data can only be entered on the negative edge of E pulsing. Could be there's a timing mismatch but it sync's up every 10 or 100 or so loop cycles, giving the delay.

[The delay is considerably smaller now that I'm running a NEC D8085AHC-2 at 4 MHz, oddly, it was the processor change and not the clock doing the big difference.]

Could also be the R/W being too fast - it's latched in the altair8800 cpu board.

Could a handshaking problem cause dead slow but correct operation?

-On a separate note, I used the memory examine/entry routine to test out the RAM, it works fine.

I'm still suspecting the E line, since that's the main enable for the chip, and is used to clock everything in it, it seems from the datasheet. using a 3x faster crystal, it should be clocked a lot more frequently, thus cycle the ACIA more often, but I'm not sure that's the right thing to look at for a problem.

It could be a timing issue with the E clocking. Perhaps inserting some equal amount of spare NAND gates as a delay would do some good.

If we assume it's a software thing (when I force-outputted, no delay), it must run in the check transmit data register empty loop. Data can only be entered on the negative edge of E pulsing. Could be there's a timing mismatch but it sync's up every 10 or 100 or so loop cycles, giving the delay.

[The delay is considerably smaller now that I'm running a NEC D8085AHC-2 at 4 MHz, oddly, it was the processor change and not the clock doing the big difference.]

Could also be the R/W being too fast - it's latched in the altair8800 cpu board.

Could a handshaking problem cause dead slow but correct operation?

-On a separate note, I used the memory examine/entry routine to test out the RAM, it works fine.

Last edited: