80186 Enthusiast

Experienced Member

- Joined

- May 18, 2023

- Messages

- 53

In my last post about my 80188 Prototyping Computer project, I realized I was getting way to ambitious for my project. I'd like to thank the following users who helped me see the errors of my ways:

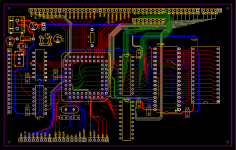

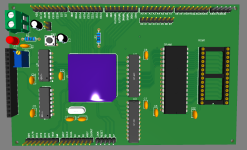

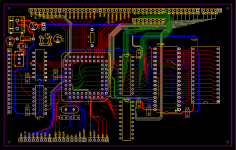

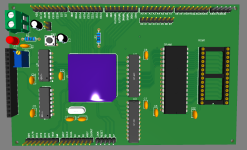

No more Multi-Master Bus, No more Intel 8288 and 8289. Just a simple barebones 80188 System board with memory that also doubles as a Breakout board as all of the CPU pins are present. This design is intended to be used with a breadboard where I'll test new hardware on with some jumper cables.

as for the hardware I'll be testing with this board, Here's a small List:

I'll make another post that showcases what I want for the future of this project sometime soon.

Thank you for reading my post, any help and advice will be thanked and appreciated in advance!

- Eudimorphodon (Thx for the sanity check)

- daver2

No more Multi-Master Bus, No more Intel 8288 and 8289. Just a simple barebones 80188 System board with memory that also doubles as a Breakout board as all of the CPU pins are present. This design is intended to be used with a breadboard where I'll test new hardware on with some jumper cables.

as for the hardware I'll be testing with this board, Here's a small List:

- 8279 Keyboard Controller

- TMS9918A Video Display Processor (Before I replace it with a Raspberry Pi Pico with VGA video)

- 8255 Peripheral Interface (PPI)

- 8041 Universal Peripheral Interface (UPI)

I'll make another post that showcases what I want for the future of this project sometime soon.

Thank you for reading my post, any help and advice will be thanked and appreciated in advance!