Don't worry, you weren't pestering. I just kept looking at it and lamenting that I didn't have the time to work on it now that I've gotten started again, especially with somebody else to bounce ideas with.

Cool. And I think it's really helped; I know I dodged a bullet by thinking out loud about those things that raised red flags in the back of my head while reading the tech manual, and it was awesome you were able to confirm them with your breadboard setup. I was *this* close to sending off a PCB order with the memory map hard-set to the wrong locations.

Are you using a Dallas DS1216 for calendar? I'm thinking I ought to add one to mine as well (especially since my SmartWatch recently died).

Yeah, or at least mostly yeah. I've got an order of five DS1315s coming on the slow boat. (It should be pin/API compatible with the older DS1215/1216. I found a source that had them for a comparable price... assuming they're actually good, of course.)

Was your plan ultimately to add the RAM to the XT-IDE board you were working on, or keep them as separate cards? If they're going to stay separate the XT-IDE board might be a more logical place for the calendar chip; you should just be able to piggyback it on the EEPROM's chip select.

Part of the reason for using the 1MB card design as the basis for my prototype was so that I could probe around and figure out if it recognized any of the UMBs, and then I'd refine it later.

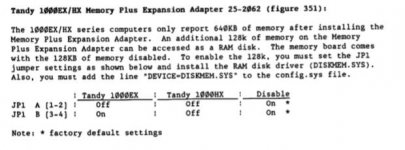

Nothing wrong with that plan, although I think at this point the Check-It results are probably enough to make an assessment. They agree with the tech manual in that with no expansions an HX has 128k of open UMB in the C000 and D000 pages. You'll need some of the C page for your XT-IDE option ROM (and it might be good leaving space for a network card), so it's probably fair to say it's D000 or bust. For an EX E000h should be open too...

(After reading that passage in the original T1000 service manual about how the initialization sequence works I'm off the idea of trying to use the A000h page. Even though Check-It says it's open that manual implied it was occupied by Big Blue at least briefly during initialization. I don't think EGA/VGA cards don't enable their A000 presence until you fire up a graphics mode so the fact that later 1000s are compatible with EGA/VGA I don't think necessarily means there wouldn't be a potential conflict if you had RAM hardwired there.)

Here's a mickey-mouse idea for enabling D000 without needed another RAM chip, but you'd need two more decoder ICs:

1: Place a 74LS138 across A16-18 with the high enable wired to A19. That will give you 64k resolution chip selects for the upper half of RAM.

2. Connect the active-low output for D000 to one input of the extra NAND on the 74LS000.

3. Connect A17 to the other lead of that NAND. Then use the output as A17 for the RAM chip.

4: Add a 74LS08 AND gate and use a gate to combine that D000 chip select with the chip select generated by the NAND decoding for the bottom 384k. Route that to the RAM chip select and the '245.

If I thought this out correctly this should work so read/writes to the D000h area are redirected to a different region of the chip than writes to 6000h, where they'd otherwise end up. (It'll also flip-flop the bottom 128k pages while it's at it, but that's fine, computer won't care as long as everything's unique.) If this works you'll get all the UMB you can have on an HX without having to add another

memory chip. Might want to double-check my reasoning, though.

(* note: if you actually went with this idea I'd also suggest AND-ing the E000h chip select with the combination select you get in step 4. This would provide the E000h UMB if your card was used in an EX. You could add jumpers/switches with pull-ups on the D000/E000h lines to allow these UMBs to be disabled.)