cosam

Veteran Member

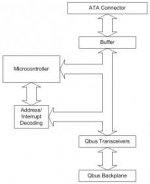

I've been thinking about putting together a Qbus MSCP to ATA/IDE adapter for a while now; mostly just brainstorming, but as my supply of remaining functional MFM drives begins to dwindle, maybe it's time to do something concrete about it. SCSI adapters tend to be expensive (if buying a commercial one) or pretty complicated to build at home. I also think it'd be really convenient to be able to use one of those handy CF/IDE adapters to put a few GB of storage right on the card. The availability of small IDE disks is also a nice bonus (yes, you can still find small SCSI disks, but they're not quite as common).

I'm aware of this similar project which looks nice. Pretty much everything is done by one big CPLD, but it would appear that you need a specific driver to talk to it. I wonder if it's feasible to emulate, for example, an RQDX3 which a lot of operating systems support out of the box. If it could also do TMSCP, you could even read and write tape images, meaning you could do full bare-metal installations.

So how much interest is there in such an adapter? I know if this was already available for a reasonable price I'd have bought/built at least one or two by now. There appears to be enough documentation out there on the Qbus and the MSCP protocol itself to design and build a working controller, but I know that if I had to do it all myself, we'd be a few years further down the line before anything resembling a functional card came to fruition. If you're at all interested in either using or possibly even contributing to the development of such an interface, please let me know.

Cheers,

I'm aware of this similar project which looks nice. Pretty much everything is done by one big CPLD, but it would appear that you need a specific driver to talk to it. I wonder if it's feasible to emulate, for example, an RQDX3 which a lot of operating systems support out of the box. If it could also do TMSCP, you could even read and write tape images, meaning you could do full bare-metal installations.

So how much interest is there in such an adapter? I know if this was already available for a reasonable price I'd have bought/built at least one or two by now. There appears to be enough documentation out there on the Qbus and the MSCP protocol itself to design and build a working controller, but I know that if I had to do it all myself, we'd be a few years further down the line before anything resembling a functional card came to fruition. If you're at all interested in either using or possibly even contributing to the development of such an interface, please let me know.

Cheers,