gwiley

Experienced Member

sorry, these are points on the +5V distribution trace to the right and left of the mounting holes. Example: H2R is to the left of mounting hole H2, H3L is to the left of mounting hole H3. The hole reference designator is in a very small font on the top side silkscreen. The reason for identifying these locations is that the +5V trace/plane gets narrow near each of the mounting holes, so the corresponding resistance lump in the model is a separate element.1. Where are points H2R, H3R, H4R, and H5R? H3L, H4L, and H5L?

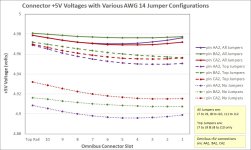

Oh, BTW, sorry again, I forgot to attach the file with voltages that LTSpice computed so you could see the final result.

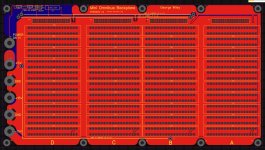

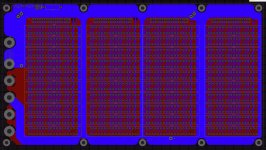

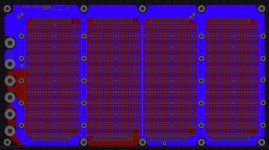

A couple of reasons: the ground plane is almost the entire top side (the red layer in the image) so it's much more robust that the comparatively narrow +5V distribution traces. But with all of the copper clearance around each of the Omnibus connector pins it reduces the effective ground plane width to about 55% of the total height of the board. So, the ground semi-plane (with 1296 holes in it) from the GND power terminal pad on the left all the way to the A2C and A1C connector pads on the right (the right-most Omnibus ground pins) is about 2.2 milli-ohms with 1 oz copper. 12 amps through that is about 26 mV, and then the ground current will actually be distributed to other Omnibus board pins, so the drop will be even less.2. It seems to me that the model needs to also add (at least) 2x 14AWG on the ground return plane when considering the effect of adding the same on the +5v distribution plane. There's not much point in fortifying just half of the +5v power circuit. Considering that the ground return plane is shared with two other power distributions IMO it's the one most subject to "droop" -- which would be in practice "raise" -- at the edge-connectors.

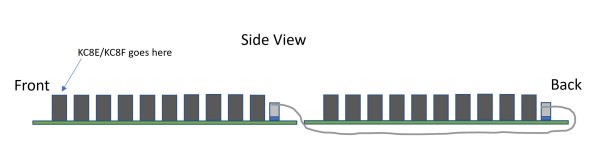

Also, the -15V current actually helps reduce the voltage drop through the ground plane because the ground current flows in the opposite direction. So, plug in more core memory and it reduces your ground plane voltage drop! +15V draws 1A max, pretty small. I measured +15V consumption to be about 0.6A on my system, and that's with the KC8E lamps powered from a regulator tied to the +15V.

In the present design the wires attach at specific points: J7 through J10, so the model reflects this. I combined the resistance of the two AWG 14 wires into R8 in the model, since J7 & J8 are close and J9 & J10 are close.3. Why not treat (and install) the added wires as a distributed drop in resistance, rather than a single point-attachment?

It would be possible to lay a thick bare wire along an extended copper area sans solder mask, but there are some issues with that: takes a lot of heat to melt solder over such a large area, adds another labor-intensive step, doesn't look so attractive. And the end result is that the reduction in voltage drop is marginally better only at certain points between what would be the wire ends. Also there are only discrete attach points of +5V to the Omnibus boards, only at pins A2A, B2A, C2A.I would strip some 14 or 12 AWG solid wire, form it to the proper "C" shape, and then solder it directly to the copper-plane, ideally continuously but certainly at multiple locations -- the idea being to closely approximate the effect of (distributed) 2oz copper. I've seen this done in various fashions in various other designs, including just being liberal in applying solder to traces to build up some thickness (not as good as pure copper, but it helps). At least I'd add wires dedicated to each of the third and fourth-ranked slot-sets rather than a single (set) added somewhere between them.

This is definitely possible and would probably reduce the +5V drop even more. Ease of assembly, cost and esthetics was pulling me in the other direction. I attached the LTSpice operating point data. Seems good enough, but feedback on that is appreciated.Pragmatically I'd focus on building up the "crossbars" that are the terminal distribution legs to the connectors through fully-soldered pieces of heavy copper wire. Particularly the one down-the-middle. Eyeballing (spitballing?) the copper distribution that's where the pinch-point looks to fall given that we're assuming an equally-distributed +5v load across the three connectors of a given module.

You're welcome.Thanks for the further enlightenment :-}.

DC operating point from LTSpice:

Code:

--- Operating Point ---

V(in_terminal): 5 voltage

V(n001): 4.97899 voltage

V(j7_j8): 4.98654 voltage

V(n005): 4.96903 voltage

V(n006): 4.96812 voltage

V(n007): 4.96477 voltage

V(n008): 4.96386 voltage

V(j6b_port): 4.99324 voltage

V(j9_j10): 4.97907 voltage

V(n002): 4.97718 voltage

V(j9ca2): 4.97286 voltage

V(j8ca2): 4.96971 voltage

V(j7ca2): 4.96709 voltage

V(j6ca2): 4.96501 voltage

V(j5ca2): 4.96347 voltage

V(j4ca2): 4.96248 voltage

V(j3ca2): 4.96201 voltage

V(j2ca2): 4.96209 voltage

V(j1ca2): 4.96271 voltage

V(n009): 4.96369 voltage

V(n010): 4.96303 voltage

V(n011): 4.96285 voltage

V(j9ba2): 4.97488 voltage

V(j8ba2): 4.97256 voltage

V(j7ba2): 4.97049 voltage

V(j6ba2): 4.96866 voltage

V(j5ba2): 4.96708 voltage

V(j4ba2): 4.96574 voltage

V(j3ba2): 4.96465 voltage

V(j2ba2): 4.9638 voltage

V(j1ba2): 4.96321 voltage

V(n012): 4.96218 voltage

V(n013): 4.95981 voltage

V(n014): 4.95914 voltage

V(j9aa2): 4.97136 voltage

V(j8aa2): 4.96733 voltage

V(j7aa2): 4.96398 voltage

V(j6aa2): 4.96129 voltage

V(j5aa2): 4.95926 voltage

V(j4aa2): 4.95791 voltage

V(j3aa2): 4.95722 voltage

V(j2aa2): 4.95719 voltage

V(j1aa2): 4.95783 voltage

V(n003): 4.97346 voltage

V(n004): 4.97336 voltage

I(R75): -3.10386 device_current

I(R74): -3.10386 device_current

I(R73): 5.35933 device_current

I(R72): 0.750314 device_current

I(R71): 0.750314 device_current

I(R70): -0.865324 device_current

I(R69): 0.440696 device_current

I(R68): -0.424628 device_current

I(R67): 0.440639 device_current

I(R66): 0.0160117 device_current

I(R65): 0.440641 device_current

I(R64): 0.456653 device_current

I(R63): 0.440703 device_current

I(R62): 0.897356 device_current

I(R61): 0.440823 device_current

I(R60): 1.33818 device_current

I(R59): 0.441003 device_current

I(R58): 1.77918 device_current

I(R57): 0.441242 device_current

I(R56): 2.22042 device_current

I(R55): 0.441541 device_current

I(R54): 2.66197 device_current

I(R53): 0.441898 device_current

I(R52): -0.865324 device_current

I(R51): -0.865324 device_current

I(R50): -0.865324 device_current

I(R49): 0.634696 device_current

I(R48): 0.441174 device_current

I(R47): 1.07587 device_current

I(R46): 0.441227 device_current

I(R45): 1.5171 device_current

I(R44): 0.441302 device_current

I(R43): 1.9584 device_current

I(R42): 0.441399 device_current

I(R41): 2.3998 device_current

I(R40): 0.441518 device_current

I(R39): 2.84132 device_current

I(R38): 0.441659 device_current

I(R37): 3.28297 device_current

I(R36): 0.441821 device_current

I(R35): 3.7248 device_current

I(R34): 0.442006 device_current

I(R33): 4.1668 device_current

I(R32): 0.442212 device_current

I(R31): -0.230628 device_current

I(R30): -0.230628 device_current

I(R29): -0.230628 device_current

I(R28): -0.946055 device_current

I(R27): 0.44113 device_current

I(R26): -0.504925 device_current

I(R25): 0.441075 device_current

I(R24): -0.0638501 device_current

I(R23): 0.441068 device_current

I(R22): 0.377218 device_current

I(R21): 0.441109 device_current

I(R20): 0.818327 device_current

I(R19): 0.441198 device_current

I(R18): 1.25952 device_current

I(R17): 0.441334 device_current

I(R16): 1.70086 device_current

I(R15): 0.441519 device_current

I(R14): 2.14238 device_current

I(R13): 0.441752 device_current

I(R12): 2.58413 device_current

I(R11): 0.442032 device_current

I(R10): -2.27585 device_current

I(R9): -2.27585 device_current

I(R8): -8.46319 device_current

I(R2): 11.9157 device_current

I(R1): 11.9157 device_current

I(R7): -1.17668 device_current

I(R6): -1.17668 device_current

I(R5): -1.17668 device_current

I(R4): 1.17668 device_current

I(R3): -3.45253 device_current

I(V1): -11.9157 device_current