PHANTOM is set by RESET forcing the flipflop's PRESET line. PHANTOM is cleared when MREQ force a CLK on the flipflop which sets the output low per the grounded input line.

Yes, there were a few thing sI noticed after I posted that

Also, we have a thread running in parallel on the MARCH group list by the same Op

And so there were a few replies that were out of sync with this thread

I reposted them from there to help complete the discussion

Glitch said:

On Tue, Sep 9, 2014 , Systems Glitch

> took a look at the schematics tonight [rev.2],

> is this the version you have ?

Yes, I've been working off of the manual from Bill Degnan's site.

> what was the addr range of that new Ram card again ?

32K from 0x0000 - 0x7FFF

> assumed you would *only* use their configuration in the system. Because

> /PHANTOM is only supposed to be asserted during a qualified memory access

> and not arbitrarily at /Reset [or /POC]. Plus the fact that /PHANTOM is

> allowed to be asserted by any card, not only the CPU card.

It seems a lot of cards did abuse /PHANTOM for POJ functionality. The ZCB still allows other cards to assert /PHANTOM though, since the 8097 that drives /PHANTOM is tristated when it's inactive. It's supposed to be open-collector, but I guess tristate is better than just straight driving the line!

> meant to say this,

> That FF operates in only one direction, either via the /reset to assert the

> /phantom signal and via the /mreq.

Right, the FF can only be /PRESET by system /RESET, and it can only be cleared by a memory access to onboard devices. However, once the FF has been cleared by a memory access, that's it, it's out of the picture. All future /PHANTOM assertions are via the other input to the NOR gate that drives the 8097 that ultimately drives /PHANTOM.

I think I'm going to cut the /PRESET line to the FF and jumper it to +5. It looks to me that the external bus receivers will be disabled during an internal device access anyway, so the board should still do POJ.

Ragooman said:

On Tue, Sep 9, 2014 at 10:01 AM, Dan Roganti <ragooman@gmail.com> wrote:

Glitch said:

On Tue, Sep 9, 2014 at 9:39 AM, Systems Glitch

> It seems a lot of cards did abuse /PHANTOM for POJ functionality. The ZCB still allows other cards to assert /PHANTOM though, since the 8097 that drives /PHANTOM is tristated

> when it's inactive. It's supposed to be open-collector, but I guess tristate is better than just straight driving the line!

oh yea, I see that its a tristate, it was just surprising to see that it was asserted immediately after a /reset

> meant to say this,

> That FF operates in only one direction, either via the /reset to assert the

> /phantom signal and via the /mreq.

Right, the FF can only be /PRESET by system /RESET, and it can only be cleared by a memory access to onboard devices. However, once the FF has been cleared by a memory

access, that's it, it's out of the picture. All future /PHANTOM assertions are via the other input to the NOR gate that drives the 8097 that ultimately drives /PHANTOM.

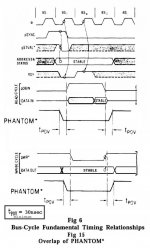

that's something else I noticed with that addr decode for the FF. And this was also looking strange. When there is a memory access to 0xE000 [with the default jumpers], the /mreq pulse will then clear the FF and the /phantom is no longer asserted [the buffer switches to tristate].

Because the /mreq signal is inverted for the addr decode, so the clock edge for the FF happens on the leading edge of the pulse from U34 inverter at the clock input of the FF. I am assuming the Jumper Area H is for True logic level selection - jumper = actual logic level - which is shown already in the schematic.

If you have a 64KB system, using a separate Ram Card, you like to keep /phantom asserted to disable that other memory card during the complete read or write cycle while accessing the onboard Eprom at 0xE000 - am I missing something on there ?

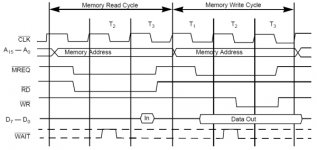

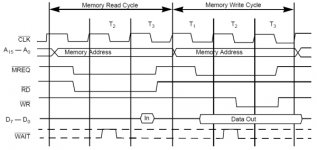

Normally, the trailing edge of /mreq signifies the end of a memory access, either read or write cycle.

But now, the /mreq gets inverted 3x times in that addr decode by the time it gets to the clock input on the FF.

The 1st inverter, the Nand, and then the 2nd Inverter

So that FF clock signal is now an inverted /mreq signal, plus a few nanosec's of propagation delay, so it's a positive pulse

The FF clock is a positive edge trigger, so the FF gets cleared on the leading edge of that positive pulse

And so the /phantom is deasserted since the buffer switches to tristate when the U28 Nor changes to HI

The leading edge happens to be the start of the memory access, not the end of the memory access.

I wasn't sure if you left the Jumper area F option for the U17 Nand decode unchanged - so that output is always a LO to U28 Nor

I inserted the Z80 timing diagram below here for reference

I didn't have a chance yet to make a timing diagram of that circuit

This is why I feel I'm missed something - if not, it looks more weird