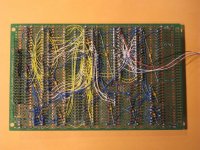

Over the last few months I finally got around to something that I have been meaning to do for many years - building a small single board computer base on a T11.

The board has 4 x 28 pin sockets that can support up to 64k of static ram and 64k of eeprom with address decoding handled by a 22v10 GAL that allows a lot of flexibility about what gets mapped where.

There are also 2 x 40 pin sockets for DC-319 serial ports and a 40 pin header for a compact flash card in an ATA bus adaptor.

Interrupt encoding etc is handled by a second 22v10 GAL.

I haven't finished wiring up the ATA bus connector or the interface logic yet, but the processor, memory and serial ports are all working.

The ultimate goal of this is to be able to run the original RT-11 version of Adventure and, possibly a few other games.

While the board should be able to run "real" RT-11 once a suitable driver for the compact flash card has been written it appears that the Mentec license doesn't apply to running RT-11 on "real" hardware so I will probably end up writing my own small monitor program that supports just enough to be able to load and run simple binaries.

Here is the current state of things:

I can supply more details if anyone is interested.

The board has 4 x 28 pin sockets that can support up to 64k of static ram and 64k of eeprom with address decoding handled by a 22v10 GAL that allows a lot of flexibility about what gets mapped where.

There are also 2 x 40 pin sockets for DC-319 serial ports and a 40 pin header for a compact flash card in an ATA bus adaptor.

Interrupt encoding etc is handled by a second 22v10 GAL.

I haven't finished wiring up the ATA bus connector or the interface logic yet, but the processor, memory and serial ports are all working.

The ultimate goal of this is to be able to run the original RT-11 version of Adventure and, possibly a few other games.

While the board should be able to run "real" RT-11 once a suitable driver for the compact flash card has been written it appears that the Mentec license doesn't apply to running RT-11 on "real" hardware so I will probably end up writing my own small monitor program that supports just enough to be able to load and run simple binaries.

Here is the current state of things:

I can supply more details if anyone is interested.