Was the serial capability a separate adapter? The page indicated there was a "legacy serial header". I'm assuming I need an adapter to do serial. I bet the adapter converts 12V logic levels to 3V. If the other 16 lines are not buffered what are they used for?

Thanks

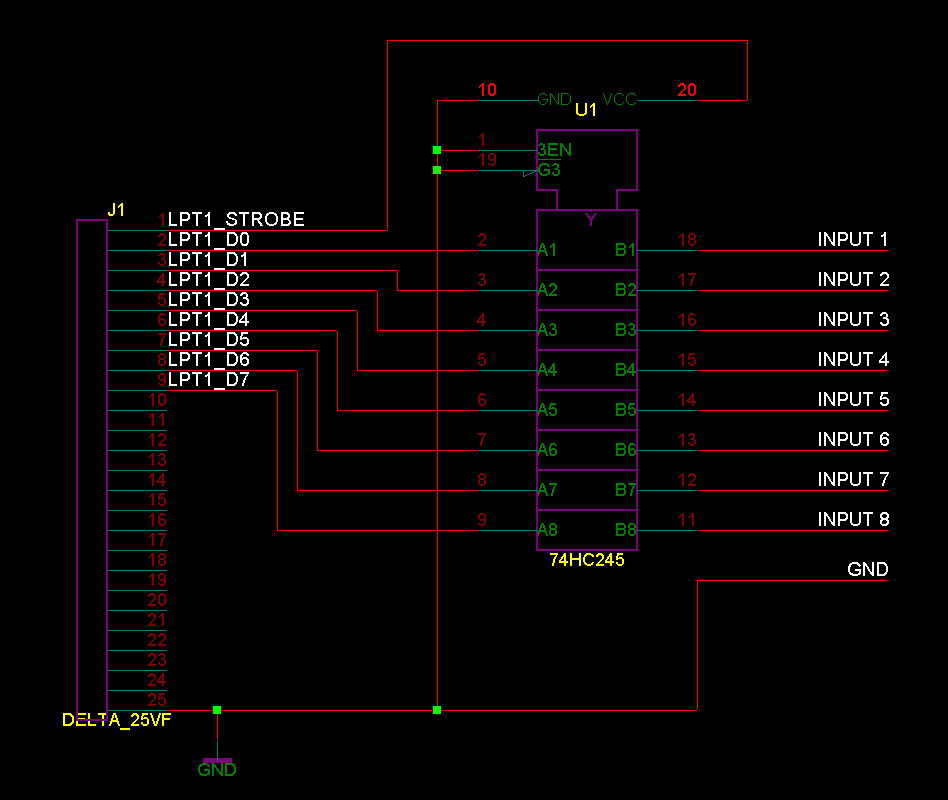

I just used 4 lines on the 16 buffered inputs to capture clock, data, reset, and bus-on signals in parallel. The other 16 lines as well as the other headers are there for expansion.

- 1x18 pin right angle header with capture lines 0-15 from the '245 buffer & 2 grounds. Any of which or a combination can also be used for trigger on a variety of conditions.

- 1x18 unstuffed header for capture lines 16-31 at unprotected LVCMOS levels

- 2 separate unstuffed 1x4 headers with 5V, 3.3V, 2.5V, & GND

- 1x4 unstuffed header with RS-232 TX & RX from the PIC, USB +5V supply, and GND

- 1X5 unstuffed header with GPIO P6C & P6D from PIC, 5V, 3.3V and GND

- 2x2 unstuffed header with separate CLKI, CLKO, TRGI, TRGO signals (all wired to PIOs on FPGA - as outputs for external logic)

- 1x8 unstuffed header with SPI clock, slave in, slave out, slave select, and 3.3V, one GPIO from PIC and GND x2.

- All headers use standard 100 mil spacing

- There are update and reset switches present

- There are power, usb activity, arm and trigger LEDs present

- The FPGA has an external 50 MHz XO, the PIC an external 16 MHz crystal. I presume both are bumped significantly with internal PLLs

- PIC is a 16F2450 in a SOIC-16 package

- FPGA is a Xilinx Spartan-3E (S250) in a TQFP-100 package

- Buffer is a Phillips LCX16245G in a TSSOP-48 package

- Micro-USB connector - cable not included