jdreesen

Experienced Member

As I have been loaned (thanks Jaak Bartok !) a Datapoint 5500, with the target of gettting it running again, I thought this might be a good spot to track progress.

The 5500 is a follow-up of the 2200, and shares the same housing. Internally it differs quite a lot from the 2200 : while ALU is almost identical, and PC/stack is very similar, though with added MMU, the control logic is very different.

The DP5500 is a microcoded machine,, with 10 256x4 proms defining the functionality. (The 2200 has hardcoded logic.)

Additionally the 5500 contains 4K of firmware code.

The 5500 shares the PSU and the display-card with late models DP2200.

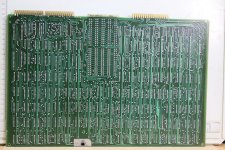

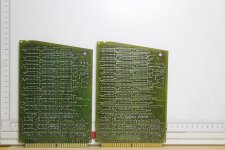

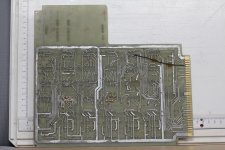

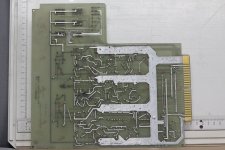

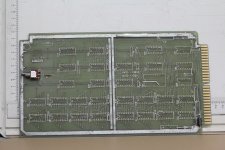

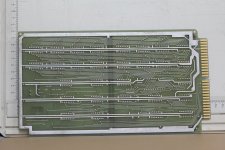

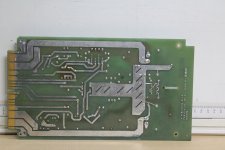

PCB pics will follow, but let me start off with some reengineered schematics and rom-recoveries.

(The .tar.txt is actrually a tar file)

Thanks to Ruud Balstissen for extensive pre-work on the schematic.

Jos

The 5500 is a follow-up of the 2200, and shares the same housing. Internally it differs quite a lot from the 2200 : while ALU is almost identical, and PC/stack is very similar, though with added MMU, the control logic is very different.

The DP5500 is a microcoded machine,, with 10 256x4 proms defining the functionality. (The 2200 has hardcoded logic.)

Additionally the 5500 contains 4K of firmware code.

The 5500 shares the PSU and the display-card with late models DP2200.

PCB pics will follow, but let me start off with some reengineered schematics and rom-recoveries.

(The .tar.txt is actrually a tar file)

Thanks to Ruud Balstissen for extensive pre-work on the schematic.

Jos