Kakemoms

Experienced Member

Hi

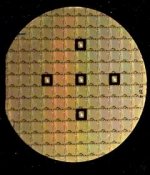

I am trying to find out more about how the different revisions of the original MOS6560 (VIC) chip was manufactured. It was designed in 1975-1977, so I guess it started out with hand layout on paper and Rubylith, but by the last batch (1984) it must have gone through some transitions. Was it digitized? Translated into VHDL? If anyone here knows anything about how MOS design and photomask manufacturing changed in the 1977-1983 period, I would like to hear about it.

I am trying to find out more about how the different revisions of the original MOS6560 (VIC) chip was manufactured. It was designed in 1975-1977, so I guess it started out with hand layout on paper and Rubylith, but by the last batch (1984) it must have gone through some transitions. Was it digitized? Translated into VHDL? If anyone here knows anything about how MOS design and photomask manufacturing changed in the 1977-1983 period, I would like to hear about it.