jonathanjo

Member

- Joined

- Feb 18, 2024

- Messages

- 38

Hi Friends

For context: I'm working on getting a PDP11/53 running: starting with the basic KDJ11-DS CPU board (main thread). As I'm currently getting somewhat unpredictable memory errors, I'm trying to find more details about how the memory subsystem is designed.

This board uses three blocks of 18 x 41256 RAM chips (datasheet) to give 1.5 MByte with per-byte parity.

These chips have a number of ways of doing refresh

I couldn't find the refresh details in the CPU doc, but as it has a full address bus I'd assume the DRAM interfacing is done by the DC7063 / DC7064 gate arrays.

Does anyone know the exact refresh strategy of this board?

Jonathan.

For context: I'm working on getting a PDP11/53 running: starting with the basic KDJ11-DS CPU board (main thread). As I'm currently getting somewhat unpredictable memory errors, I'm trying to find more details about how the memory subsystem is designed.

This board uses three blocks of 18 x 41256 RAM chips (datasheet) to give 1.5 MByte with per-byte parity.

These chips have a number of ways of doing refresh

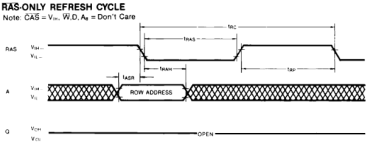

- CAS-before-RAS with internal row-counter

- RAS-only

- "Hidden" (CAS-before-RAS embedded in a read)

I couldn't find the refresh details in the CPU doc, but as it has a full address bus I'd assume the DRAM interfacing is done by the DC7063 / DC7064 gate arrays.

Does anyone know the exact refresh strategy of this board?

Jonathan.