Mike_Z

Veteran Member

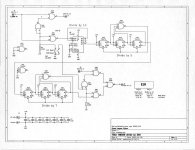

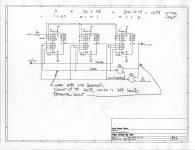

I use a M8650 serial board in my real PDP8e. The terminals that I use is either a CIT-101 at 9600 baud or an ASR33 at 110 baud. My issue is that in order to change from the CIT-101 to the ASR33 I also have to pull the M8560 board and replace it with one that works at 110 or 9600 baud. For the past few weeks, I've been thinking about how to add something to the M8650 board so that I can just use a switch to change the baud rate. The problem is that 110 baud is not a factor of the 9600 family of frequencies. After looking at the M8650 schematic, it appears that the 9600 board has a 1.9661 Mc clock. This is divided down to 153.6 Kc and 19.2 Kc for the board to use 9600 baud. Trying to figure how to use these for 110 Baud

19.2 Kc/110 = 174.55 can not get 1/2 divide

38.4 Kc/110 = 349.09 this is pretty close to 349

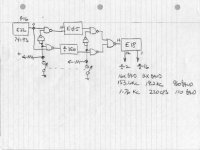

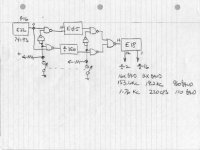

I figured that if I could insert a divider of 349 in the division line I could get the 1760 and 220 cycles needed to generate 110 baud. Problem is that 349 is a prime number, making it difficult to build a divider. Then I thought that how about using a divider of 350 and place it at a higher frequency spot in the division line. If I use the 1.2288 Mc (E22 pin 7) as the input of my 350 count divider and connect the output of my 350 divider to pin 14 of E18 I could get really close to 110 baud

1.2288 Mc/350 (new 350 divider) = 3.511 Kc / 16 (existing E18) = 219.43 cps

This is really close to the needed 220 cps for 110 baud. So, I figured using a 7490, divide by 10, then a JK flip flop divide by 5, followed by a JK flip flop divide by 5. Then with a toggle switched control circuit the would connect the original counters into the circuit for 9600 baud or switch out the original counter for the new 350 counter circuit.

Do you think this should work? Thanks MIke

19.2 Kc/110 = 174.55 can not get 1/2 divide

38.4 Kc/110 = 349.09 this is pretty close to 349

I figured that if I could insert a divider of 349 in the division line I could get the 1760 and 220 cycles needed to generate 110 baud. Problem is that 349 is a prime number, making it difficult to build a divider. Then I thought that how about using a divider of 350 and place it at a higher frequency spot in the division line. If I use the 1.2288 Mc (E22 pin 7) as the input of my 350 count divider and connect the output of my 350 divider to pin 14 of E18 I could get really close to 110 baud

1.2288 Mc/350 (new 350 divider) = 3.511 Kc / 16 (existing E18) = 219.43 cps

This is really close to the needed 220 cps for 110 baud. So, I figured using a 7490, divide by 10, then a JK flip flop divide by 5, followed by a JK flip flop divide by 5. Then with a toggle switched control circuit the would connect the original counters into the circuit for 9600 baud or switch out the original counter for the new 350 counter circuit.

Do you think this should work? Thanks MIke