I read this old post about EGA: https://forum.vcfed.org/index.php?threads/ega-video-corruption.43557/post-585123

So does this mean all emulators are wrong?. I can't test a real EGA.

Thanks.

I tried modifying EGA PEL panning without waiting for vsync, and my attempt to make a wave effect failed (Dosbox, PCem, 86Box)....

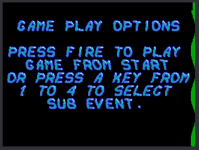

On EGA and the Paradise PVGA1A, and maybe others, display start is latched at the falling edge, and PEL panning is NOT LATCHED AT ALL. PEL panning can be updated while visible scanlines are put out and the change is seen immediately (or at scanline start). The game Beverly Hills Cop (by Tynesoft) uses this to show a screen with text with sine wave effect. This works on EGA but not on VGA (except on the Paradise card).

...

So does this mean all emulators are wrong?. I can't test a real EGA.

Thanks.