Activmaker

Experienced Member

Hi,

In 1995 during learning session, I discovered PDP-11 architecture and programmation. I liked it a lot. Since few years now , I search to get my own PDP. I wanted a unibus machine not Qbus. A 11/70 or 11/45 would have been perfect , but I didn't find something interesting. Last year I thought :"Is it possbile to build one from scratch ?". So, I start to read and read and read again DEC documentation (Thanks to bitsavers guys !) . I also learned to make PCB boards and re-learned electronic (I learned basic electronique around 1988 ). Around july 2018 , I decide to really start the study. I choose 11/45 for 2 reasons:

1) 11/70 is a little bit complex fo me.

2) I like the concept of Unibus B in 11/45.

My goal is to keep the "spirit" of PDP11. Mes requirements are :

1-My boards must be run into a real PDP.

2-My PDP can use boards of real PDP.

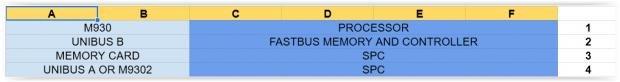

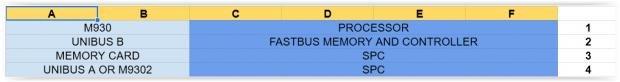

I studied an hardware architecture and finnaly I decided to have (for the first "shoot") this backplane architecture :

Today I plan to use a brige between row 2 and row 3 to use dual port memory.

The actual state of this project is

1 M930 and 1 M9302

1 Test board for SPC . The board helped me to debug wrapping of backplane. I use it to visualize the signals and put an logical analyzer.

1 CPU Board (Will emulate KB11A +MMU+FP). On right part there is 2 connectors for the console. Switch on board can activate or not some parts (MMU/FP/M9312). CPU can use external LTC signal or use an internal clock. An connector is present to connect a USB terminal (MobaXterm in my case) . Not in the "spirit" of PDP 11 .

.

Few G227 Boards.

Of course a backplane has been made.

All boards:

On the top left the memory board with 128Kw. Some bugs was found in it , I modified PCB routing using wiring and cutter !.

An other small board has been made to filter the power supply, give a 3.3v and simulate sequence of ACLO and DCLO.

Terminators,bus control,Memory board seems to works correctly. CPU Test are not finished yet but as far as now all tested parts work.

Today I decided to show you this year of work.

And now ? Of course I will ontinue on it, I already know that I will make a new CPU board ,but this one will ge me a lot of work!. I am studying also a RL11 SPC board (With 4 emulated RL02).

I let you to comment this project maybe you like , maybe not...

Thank you for reading me to the end

In 1995 during learning session, I discovered PDP-11 architecture and programmation. I liked it a lot. Since few years now , I search to get my own PDP. I wanted a unibus machine not Qbus. A 11/70 or 11/45 would have been perfect , but I didn't find something interesting. Last year I thought :"Is it possbile to build one from scratch ?". So, I start to read and read and read again DEC documentation (Thanks to bitsavers guys !) . I also learned to make PCB boards and re-learned electronic (I learned basic electronique around 1988 ). Around july 2018 , I decide to really start the study. I choose 11/45 for 2 reasons:

1) 11/70 is a little bit complex fo me.

2) I like the concept of Unibus B in 11/45.

My goal is to keep the "spirit" of PDP11. Mes requirements are :

1-My boards must be run into a real PDP.

2-My PDP can use boards of real PDP.

I studied an hardware architecture and finnaly I decided to have (for the first "shoot") this backplane architecture :

Today I plan to use a brige between row 2 and row 3 to use dual port memory.

The actual state of this project is

1 M930 and 1 M9302

1 Test board for SPC . The board helped me to debug wrapping of backplane. I use it to visualize the signals and put an logical analyzer.

1 CPU Board (Will emulate KB11A +MMU+FP). On right part there is 2 connectors for the console. Switch on board can activate or not some parts (MMU/FP/M9312). CPU can use external LTC signal or use an internal clock. An connector is present to connect a USB terminal (MobaXterm in my case) . Not in the "spirit" of PDP 11

Few G227 Boards.

Of course a backplane has been made.

All boards:

On the top left the memory board with 128Kw. Some bugs was found in it , I modified PCB routing using wiring and cutter !.

An other small board has been made to filter the power supply, give a 3.3v and simulate sequence of ACLO and DCLO.

Terminators,bus control,Memory board seems to works correctly. CPU Test are not finished yet but as far as now all tested parts work.

Today I decided to show you this year of work.

And now ? Of course I will ontinue on it, I already know that I will make a new CPU board ,but this one will ge me a lot of work!. I am studying also a RL11 SPC board (With 4 emulated RL02).

I let you to comment this project maybe you like , maybe not...

Thank you for reading me to the end