modem7

10k Member

In the datasheet for the 82284 is:Maybe your procedure is correct and we're still after the root cause of the problem. Though, now that I know the boot process a little better, I don't understand why just grounding I/O CH RDY would stop the CPU starting to execute the ROM code on a 5162 since it would still get a ready signal via /SRDY when accessing the ROM (for 0xFE0000-0xFFFFFF, WAIT0 is high) (on a 5170, the /SRDY signal is just tied high).

My translation of that (written in a way that I prefer) is:

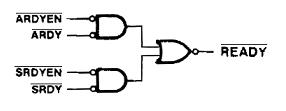

/READY is LOW when either of the following conditions is true:

Cond #1: [/ARDYEN plus /ARDY are both LOW]

Cond #2 [/SRDYEN plus /SRDY are both LOW]

Which means that for /READY to be HIGH (what we want for the 'ground I/O CH RDY' procedure), both of the following conditions need to be true:

Cond #1: [/ARDYEN is HIGH] or [/ARDY is HIGH]

Cond #2: [/SRDYEN is HIGH] or [/SRDY is HIGH]

In the 'ground I/O CH RDY' procedure, /ARDYEN and /SRDYEN are LOW. Which means that both /ARDY and /SRDY will need to be HIGH.

It fits with your experiment of, "I tested tying DWAIT0 to ground with a 25ohms resistor (pin 18 on U14) and now the CPU behave has expected on reset with the ground I/O CH RDY procedure." That would have resulted in /SRDY being HIGH.

(As you stated before, on the IBM 5170, the /SRDY pin is tied high via a resistor.)

Does that all sound right ?