OK. Diligent sell a very convenient JTAG cable as well, although somewhat more expensive than Chinese boxes: https://store.digilentinc.com/jtag-hs2-programming-cable/The notable omission on the board is the lack of programming hardware to download the FPGA design; there is a JTAG connector but you need an external programmer device to drive it. In my case I bought I programmer (also from ebay), it works well and enables to use these low cost FPGA boards. I have a few more expensive boards which have built-in programming circuitry, but I think I prefer these cheap boards especially when messing with breadboard wiring - if the smoke decides to come out, the damage will be smaller...

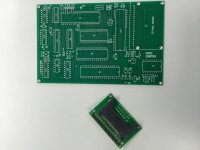

It looks like this board can be piggy backed onto another PCB -- my eyes are too old to solder anything below 0.1" I think. Are those GPIO connectors on both sides, i.e. some 80 I/O pins freely available?

Are you running the system at 3.4V? Or a bit more to be stable, 3.6V or so? Does it still run at 3MHz (12MHz crystal)?But to come back to this design, once I realized that level converters would not be necessary,

Yes, I'd be interested. Would it make sense to host the VDHL source at GitHub or so? That way there is a clear development history available for future readers. I've been thinking about learning VHDL for years but never got around to it. Perhaps 2016 will be the year.If you're interested I can post the VHDL code; although I have to say I'm not an expert on VHDL. (Getting things to work has been good enough for me... I'm much more a C++ / assembly guy, but you just cannot use those skills alone to create hardware.)

Actually, the mini Cortex board already has a socket for the "F18A", a custom breakout board with a Xilinx XC3 FPGA and a few level shifters, that implements a 9918 chip with VGA output. Later versions also include a 9900 core. The F18A is the brain child of Matthew Hagerty: http://codehackcreate.com/Also I think it would be a nice exercise to implement TMS9918 functionality, and perhaps emulation, which would enable this thing to transform both into an "actual" Cortex and TI99/4A.

I'm not sure it is open source, but it might be.

Yup, my thinking exactly.I also happen to have one TMS99105 chip. I'm very intrigued of the idea of hooking it directly to an FPGA, so that the address demultiplexers and memory buses could just exist inside the FPGA - there would be a lot less wiring that way.

Currently there is a pretty complete V6 Unix port for the mini Cortex. It could also run on a real Cortex, as long as it has been extended with a hard disk. The source code repository is here:I think I am going to need some help to get your Unix running - although I have not yet extensively read this great thread, so I don't really have an idea on how much ground has already been covered in the messages. Anyway I want (and probably need) to get some kind of mass storage working first, and I also want to get more familiar with Stuart's port of the firmware.

http://1587660.websites.xs4all.nl/cgi-bin/9995/timeline

I guess I have not documented how to get from source to a disk image, but that is easily explained once you get to it.

The disk I/O routines were a later add on to Cortex Basic. We did some work on reconstructing the source code (disassembly + new comments) about one year ago; it is in this thread. Yes, from my perspective integrating this into the ROM is very useful.As a simple but hopefully useful exercise I was planning to add to Cortex basic save&load functionality to the Flash rom. The basic interpreter is a pretty handy hardware testbed.

Paul