tschak909

Experienced Member

I am in the middle of getting the world's only video about The Frob, a 2600 gamedev system for Apple2, produced.

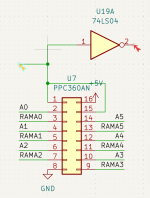

I am at the point where the hardware needs a good reverse engineering, in particular four chips that are privately labeled (PPC350AN), but all have different packages.

As I have CP, I can't do the physical bits needed to do things like removing chips and toning out pins. This is doubly important as this is an exceptionally rare card.

So I'd like to see if someone could help to be my hardware counterpart to reverse engineer this card to document it?

-Thom

I am at the point where the hardware needs a good reverse engineering, in particular four chips that are privately labeled (PPC350AN), but all have different packages.

As I have CP, I can't do the physical bits needed to do things like removing chips and toning out pins. This is doubly important as this is an exceptionally rare card.

So I'd like to see if someone could help to be my hardware counterpart to reverse engineer this card to document it?

-Thom