I worked on the 11/74 project back in the day when I was still at DEC. Writing microcode (one of three people) for the 11/74 CIS Commercial Instruction Set option.

There were actually two ongoing enhancement projects for the 11/70 going on at the time:

(1) the 11/70mP project, which used basically OTS 11/70 boards, with the small tweak to the ASRB microcode for an atomic operation. Also implemented

was something called the IIST module, which stood for IIRC Interprocessor Interrupt and Sanity Timer. It allowed for CPUs interrupting other CPUs for messaging.

(2) the 11/74 project, which was the addition of a high performance implementation of the PDP-11 Commercial Instruction Set, supporting character string

moves, decimal arithmetic and the like. Supported thru the PDP-11 COBOL compiler at the time. IIRC there were three hex logic boards added to the 11/7x backplane

for the CIS hardware. Some RH11 slots were removed to make the backplane the same physical size as the older 11/70 backplane. Technology was basically the same,

a mix of some etch but mostly wirewrap. A few CPU cards were updated with new logic to provide access into the CIS hardware.

After finishing the design and doing an engineering release on the 11/74, DEC product marketing decided not to pursue selling the 11/74 CIS variation.

Ostensibly the reason was it cost too much to make, it did not cost reduce the 11/70 (but IMHO that was not an original goal). My view was that we did

too good a job in implementing a high performance commercial instruction set. Much better than the 11/780 could do at the time. And that was the reason

for the death of the 11/74. DEC was pushing customers to VAX at the time (this late 70s early 80s) and did not want them to stick with 11/70s. Others cite

other reasons but I know what we talked about over coffee and why the 11/74 got the axe.

I think there are several 11/74 project related documents on bitsavers now (1174sysEvalPlan_Jun79.pdf, Prelim_KB11-E_Diffs_Aug78.pdf).

Ultimately DEC took the 11/74 moniker and reused it for marketing the 11/70mP product, which was just a bog standard 11/70 with the updated ASRB microcode

and the IIST option.

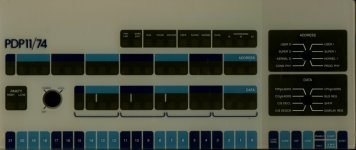

Here is a scan of the plex front panel I saved from an actual 11/74 that has the CIS option. Note the extra selections for the DATA switch:

.

.