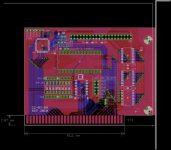

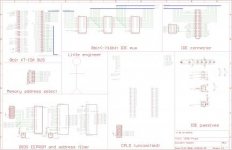

This is the schematic for an XTIDE-compatible XT IDE board. The big difference between this and the XTIDE v1 is that the control logic is built into a single CPLD chip. CPLDs are reprogrammable logic chips that can contain dozens or hundreds of 7400-series style logic. This is a developer friendly board because we can test new designs by uploading a new image, instead of choosing logic chips, routing boards, making PCBs, etc. Later, successful designs can be reimplemented in discrete, through hole logic ICs.

My goal was to fit the entire thing into a big CPLD or FPGA (including bios EEPROM), but there just aren't many 5v parts left. This led to a design for a level-translated universal-bus (XT, Amiga, PCjr, etc), do-all design with a FPGA, but that's for another post. This design uses a small 5V Xilinx FPGA that's still widely available (kind of), and is only $4 in 1sies.

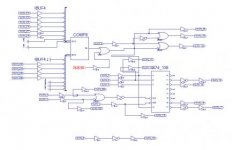

This is the XTIDE drive logic implemented in the CPLD. It uses less than half the available resources, so further improvements are definitely possible.

While the control logic can be changed on the fly, the hard connections cannot. Please let me know if there are other bus pins that would be helpful involve in the logic. DMA? There are a couple free pins on the CPLD, but not many.

Last edited: