JonB

Veteran Member

An arcane question for you all.

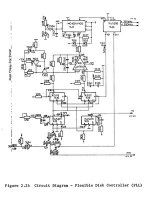

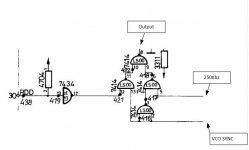

I have a Philips P2000C with a broken floppy drive interface. It uses the NEC uPD765 FDC chip, and this has an output on pin 24 called VCO Sync. It is used to bracket the RDD pulses coming off the drive.

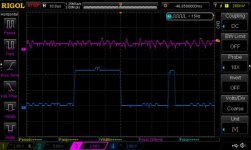

Now on mine, it is low all the time (it's supposed to go high before each read data pulse, then low after). However, I swapped the FDC into a known working machine that uses the same chip and proved it is working, so something else is not right with the P2000C.

My question is, how does the FDC generate VCO? What inputs does it use to synthesise the signal? I know it has a programmable delay (to wait for the heads to settle down after loading) before it kicks in, but mine is contestanly low and I can't see why.

Any ideas?

I have a Philips P2000C with a broken floppy drive interface. It uses the NEC uPD765 FDC chip, and this has an output on pin 24 called VCO Sync. It is used to bracket the RDD pulses coming off the drive.

Now on mine, it is low all the time (it's supposed to go high before each read data pulse, then low after). However, I swapped the FDC into a known working machine that uses the same chip and proved it is working, so something else is not right with the P2000C.

My question is, how does the FDC generate VCO? What inputs does it use to synthesise the signal? I know it has a programmable delay (to wait for the heads to settle down after loading) before it kicks in, but mine is contestanly low and I can't see why.

Any ideas?