I did have a simple thought: it's possible the problem is not the RAM at all.

I believe the RAM tests are the first thing that make use of the high byte data lane. The low bits are probably okay, at least for reading, given that you're able to read the entire ROM (byte by byte) without issue.

Maybe you have a bad bus transceiver in the high data byte?

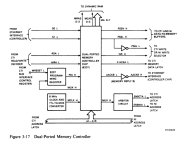

And yes, maybe the DPRAM controller is bad.

Schematics would be really, really nice (anyone out there have them??)

Yes, you can absolutely write a standalone program to test the RAM yourself.

And yes the board is accessible. You can read/write its registers in the CTI slot it's assigned to, even if it failed diagnostics, then you can tell it to map itself at some physical address and then set up your PAR/PDRs to give you virtual address access to it.

I believe on completion of the boot-time diagnostics, on success or failure, it will remove itself from the physical addressing space, so you'll need to remap it yourself.

For some of my testing what I made a cable that turned on the "maintenance mode" (a cable that shorts pin 9 to ground).

This allowed me to send a break over the serial line to put the machine into ODT mode.

Then I wrote some Python code to download little bits of code directly into RAM. The code would run and report results over the serial port.

This is how I examined some of the functionality on the DECNA when I was writing my emulator.

Most useful for you would probably be exp04.mac. This program finds the DECNA board, maps the DECNA DP RAM and writes to it.

It's been several years, so my memory is a little rusty, but you're welcome to this stuff. I'm skipping the Python code because it is really tied to the terminal emulator I was using (SecureCRT).

BTW you might try Jörg Hoppe's PDP11GUI (

https://www.retrocmp.com/tools/pdp11gui) to talk to the serial port. I think I got it to work with my PRO (I can't remember if I was using the 350 or the 380). I do remember it required me to pull some RS-232 signal up to get it to work at all (was it DTR?). But if you got that going you'd be able to download code over the serial port.

--Bjoren