8008guy

Veteran Member

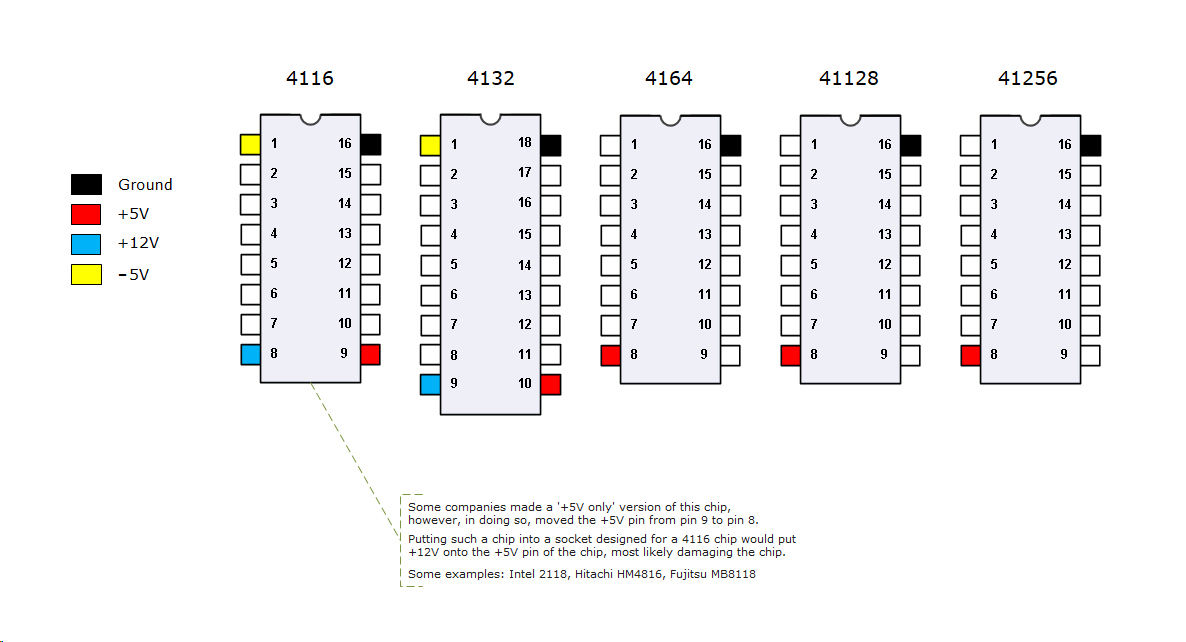

I threw this DRAM tester together today. It's for 41256 DRAMS, although it should work for 4164's as well. It's based on a bread-boaded Arduino UNO. (ATMEGA 328P) It runs four different test loops, all zeros, all ones, alternate 0's and ones and then alternate 1's and zeros. Three LED's will indicate the status, and then it will continue to loop. There is a serial port in the design, I use it for uploading the program. But it could be used to print out info as the program runs.

Schematic and Source at this link:

http://www.chronworks.com/DRAM/

I tested this with a 41256 and it runs fine. I watched all the signals on a logic analyzer and the timing appears to be good.

The only things that I'm not quite clear on is the refresh cycle. The chip specs out a 4ms refresh cycle. My RAS loop takes around 14ms to cover 0 to 511 rows. Am I understanding the data sheet correctly? Or am I covering the refresh ok? All the tests complete with no failures.

If anyone has a compelling reason why this is running too slowly I can jettison the Arduino environment and just do straight AVR, though without trying it I'm not sure how much I will gain. Anyway... I am rambling at this point. :bigups:

I'm going to find some 4164's to test as well.

Please play around with it. If you make it better let me know so I can update the project files.

len

Schematic and Source at this link:

http://www.chronworks.com/DRAM/

I tested this with a 41256 and it runs fine. I watched all the signals on a logic analyzer and the timing appears to be good.

The only things that I'm not quite clear on is the refresh cycle. The chip specs out a 4ms refresh cycle. My RAS loop takes around 14ms to cover 0 to 511 rows. Am I understanding the data sheet correctly? Or am I covering the refresh ok? All the tests complete with no failures.

If anyone has a compelling reason why this is running too slowly I can jettison the Arduino environment and just do straight AVR, though without trying it I'm not sure how much I will gain. Anyway... I am rambling at this point. :bigups:

I'm going to find some 4164's to test as well.

Please play around with it. If you make it better let me know so I can update the project files.

len