modem7

10k Member

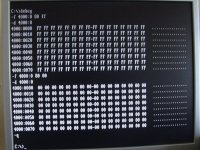

Background: Fictional example at [here].So I think to resolve the original question of the thread we can safely say that any standard 9 chip 256kB SIMMs will do

But what if some of the 9-chip 256KB SIMM's contain chips requiring 512 refresh recycles (rows) !

On a 9-chip 256KB SIMM, each of the 9 chips contains 262,144 cells (256Kbit). It is up to the chip maker as to the dimensions of the 262,144 cell matrix, e.g.

* 512 rows by 512 columns

* 256 rows by 1024 columns

If the chip's cell matrix is 512 rows by 512 columns, then the chip will require 512 refresh recycles (rows). Maybe such 256KB SIMM's do not exist. I do not know.

And so I think, to be safe, that the SIMM requirement is best put at: industry-standard 30-pin, of 256KB, with parity, of 150ns access time (or faster), of 256cycle/4ms refresh