Hi All;

Dave, Thanks for the next set of Tests and the Test from the Posting after this Post and for the Complement..

I have to get a few things done around here, I am not sure How long it will take, So it will be after I get things done..

I Think I am Done, I will know tonight.. The last few days the Heater has been running excessively and so today, I hopefully sealed the Cold Air leak(s) here in the kitchen..

"" Looking good there Marty...

The CLA/CLL occurs first (if the bit(s) is/are set) and should occur in CP0.

The CMA/CML occurs second (if the bit(s) is/are set) and should occur in CP2.

The IAC occurs third (if the bit is set) and should occur in CP3.

RAR/RTR/RAL/RTL then occur last in this order during CP4,5,6 and 7.

So, if the CLA bit is set - the ACCUMULATOR will always be cleared during CP0. To test this, load any value into AC (using LDAC) and then 'CONT' the PDP-8 machine with your desired instruction. AC should be cleared as expected.

If the CLA bit is not set, then whatever is in the ACCUMULATOR at the beginning of the instruction will be modified by the instruction.

YES..

As the instruction 'loops' this will cause the value in the ACCUMULATOR to be modified in a known pattern. So for example, CLA + IAC (7201) should guarantee that AC is cleared first in CP0 and then INCREMENTED in CP3 - so the value in AC will be 0001 after execution of the instruction (irrespective of what was in AC prior to the CONT button being pressed).

YES..

Processing IAC (7001) on its own, however, will cause the value in the accumulator to be incremented once on each execution of the instruction - so the AC value could start off at 0000 and increment to 777 and then wrap around to 0000.

YES..

Combining some of the instruction bit patterns will result in specific values in the ACCUMULATOR (taken from

http://homepage.cs.uiowa.edu/~jones/pdp8/man/mri.html and

http://homepage.cs.uiowa.edu/~jones/pdp8/man/micro.html ..

CLA (0)

YES..

CLA IAC (1)

YES..

CLA CLL CML RTL (2) CLA, 7200 : CLL, 7100 : CML , 7020 : RTL, 7006..

This Works !!

CLA CLL CML RTR (1024) CLA, 7200 : CLL, 7100 : CML , 7020 : RTR, 7012..

I Think This Works..

CLA CMA CLL RAR (2047) CLA, 7200 : CLL, 7100 : CML , 7020 : RAR, 7010..

This shows Bit '0'..

CLA CLL CML RAR (2048) CLA, 7200 : CLL, 7100 : CML , 7020 : RAR, 7010..

This Works !!

CLA CMA (4095) CLA, 7200 : CMA, 7040..

All Ones, except the Link Bit..

CLA CMA CLL RAL (4094) CLA, 7200 : CMA, 7040 : CLL, 7100 : RAL, 7004..

The Link Bit and all of the Bits, Except for bit 11..

CLA CMA CLL RTL (4093) CLA, 7200 : CMA, 7040 : CLL, 7100 : RTL, 7006..

The Link Bit and all of the Bits, Except for bit 10..

The number in the () is the (decimal) number that should be stored in the ACCUMULATOR at the completion of the instruction. To determine the instruction bit pattern, logically 'OR' the octal number for each of the separate instructions together:

CLA IAC = 7200 'OR' 7001 = 7201.

YES..

You will also find some 'wierd' instruction patterns. For example, CLA CMA IAC = 7200 'OR' 7040 'OR' 7001 = 7241. This instruction should clear the ACCUMULATOR in CP0, Then complement the ACCUMULATOR in CP2 and then increment the ACCUMULATOR in CP3. Net result, the accumulator should be cleared at the conclusion of the instruction irrespective of the value in the ACCUMULATOR at the start...

NO, But, Each Instruction works individually, But, not together..

I have ohmed out each Individual Instruction, and they are each at the Correct CPxx time..

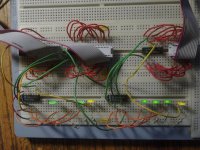

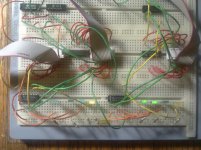

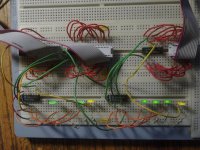

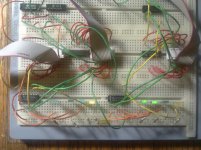

I suspect a Bad or marginally Bad IC, I am going to put it on the BreadBoard, with Lots of Leds, to see who is not getting thru correctly..

Dave, I know 'What' I should get, it's Just not happening.. I think I can find it.. I will let You Know what I find..

I see the Problem, there isn't enough time, between CP02 and CP03 for the gate to switch back after the pulse,

I am going to try and Delay Cp03 and see if that makes any difference..

No, it doesn't, I will have to bring out the other IC tomorrow morning, to see if the other IC something is holding the signal for too Long..

Dave, I have E12 and G1 on one IC, and G15 is the one I already brought out.. These are on the AC(L) schematic..

Lots of stringly wires on the BreadBoard and more Leds..

I would suggest becoming familiar with the OPR Group 1 instructions and how they operate, trying to identify what should occur, testing them out on the PDP-8 and seeing if they fit with your understanding. If not, report back what you are trying to achieve and the conflicting results you are getting and I will try and dispel the mists so to speak.

I am working on the OPR Group 2 tests now - but these are a bit more complex than the Group 1 tests... ""

GREAT !!!!!!!!!

Go ahead and Post them, when You have them ready, Even if I haven't gotten to these Tests, More Input..

I don't know, But, I suspect that these Group 2 Tests, will be the next big trouble, But, then again it could be Memory related..

Since it passed the RAR and RAL at least through the Instruction Register..

"" The non-skip part of the Group 2 instructions... I will work on the SKIP part of the Group 2 instructions and post later when I get a bit of time myself.

STOP and CLEAR buttons (this should be automatic now on power-up!)

Load 7402 into IR manually.

Load 1234 into AC manually.

Load 0000 into PC manually.

CONT.

The PDP-8 should halt with the PC advanced from 0000 to 0001. The AC should still have 1234 in it. This is the intended action because a 7402 instruction is HLT...

YES..

CONT.

The PDP-8 should halt once again with the PC advanced from 0001 to 0002. The AC should still have 1234 in it.

YES..

Try a few more CONTs. The PC should increment by 1 every time but the AC should retain 1234.

The MA Register follows the PC Register..

Load 7612 into IR manually.

CONT.

The PDP-8 should halt again (with the PC incremented by 1 again from the value before CONT was pressed) but the AC should have been cleared to 0000. 7612 = CLA HLT.

YES..

Load 7614 into IR manually.

CONT.

The PDP-8 should run continuously this time (there is no HLT bit set). 7614 = CLA OSR.

The value entered onto the handkeys should appear in the ACCUMULATOR. The PC should increment by 1 for each instruction executed.

YES, I checked each Bit Individually..

STOP.

Clear the hand keys to 0000.

Load 0000 into AC manually.

Load 7404 into IR manually.

CONT.

The PDP-8 should run continuously this time (there is no HLT bit set). 7404 = OSR.

When a handkey is set to '1' the corresponding bit should be set in the ACCUMULATOR. When the hand key is set to '0' the corresponding bit in the ACCUMULATOR should remain a '1'. This instruction OR's the hand keys with the ACCUMULATOR and stores the result in the ACCUMULATOR. ""

YES..

THANK YOU Marty