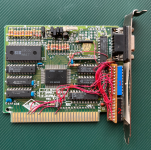

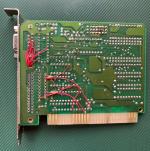

@Eudimorphodon, your assumptions were correct.

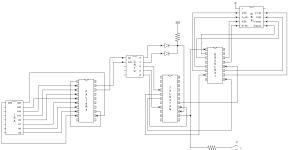

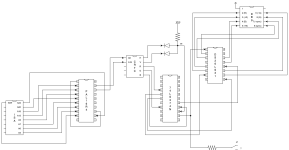

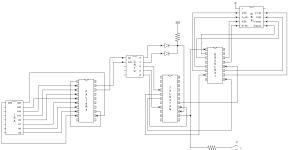

After following the traces using a multimeter, I got these schematics:

Some conclusions can be taken from the above diagram:

1 - HSYNC and VSYNC are combined into CSYNC, which then goes to 74LS374 latch.

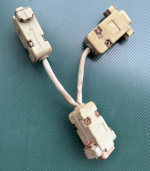

2 - The card is sending R, G, B and CSYNC through DB connector, using differential lines (R, ~R; G, ~G; B, ~B, CSYNC, ~CSYNC).

3 - PLD is only used to change card default ports and memory addresses

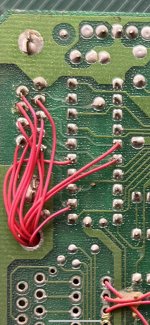

Traces A6 and A16 going through CRTC ASIC and ISA connector have ben cut off, and new connections were made from PLD. And taking into account tat the default CGA buffer addresses is

0xB80000, we should be able to deduce the new address by changing bit

A16:

And

0xA8000 is what was found by Checkit as Hi RAM, so it makes sense.

Same thing with CGA ports:

0x3D4,

0x3D5,

0x3D8,

0x3D9:

And those will become:

0x9D4,

0x395,

0x398,

0x399 after changing bit

A6

That information should be enough to try to initialize the card. For that, I grabbed

vcol.asm example from "PC System Programming" (Thanks

@modem7 for sharing the PSP floppies), that can be used to write to CGA card without using the BIOS; and then I changed the default addresses:

CONTROL_REG = 0398h ;Control register port address

CCHOICE_REG = 0399h ;Color select register port address

ADDRESS_6845 = 0394h ;6845 address register

DATA_6845 = 0395h ;6845 data register

VIO_SEG = 0A800h ;Video RAM segment address

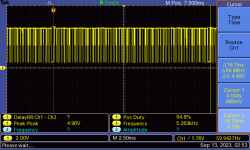

After compiling and linking with MASM, I tried it out first with DOSBOX (I compiled two versions, one using the default address and another one with the new ones):

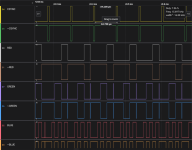

That's the pattern that should be generated by the modded CGA card.

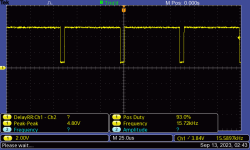

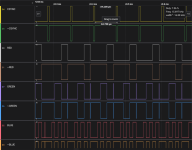

Next step was to run that on a real PC with the modded CGA card inserted. I immediately got some signals out from DB connector:

And then I captured a single frame (1 HSYNC period) and tried to render it; and I got the expected pattern in 8 colors (no intensity bit):

There are some errors in the image, probably because I have a bug in my capturing/rendering script.

There is only one thing left to figure out: I don't know the purpose of that line connecting CSYNC to

J1 jumper. If somebody has the jumper documentation for this card, it will be very useful to understand what is going on there.