Welcome to Board #1!

[Link to Original Thread / Board #3]

Here's what I know so far:

- Motherboard type 64KB-256KB

- Known good CPU inserted

- Known good RAM populated in Bank0, other banks unpopulated

- RDR Doesn't boot up, no beep, LPT says "00" and nothing more

- Booting with known good BIOS, no beep, no video

- Verified power supply

- Verified 4.77 MHz clock

- No pulses on pin 13 of the 8253 chip

Performed The 'ground I/O CH RDY' Procedure, this is what I see:

8088's READY (22) and RESET (21) pins are LOW

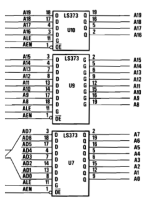

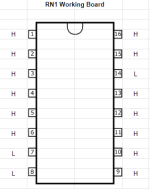

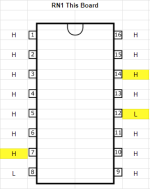

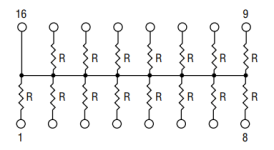

A0 H

A1 H

A2 H

A3 H

A4 H

A5 H

A6 H

A7 H

A8 H

A9 -

A10 L

A11 L

A12 H

A13 -

A14 -

A15 -

A16 H

A17 H

A18 H

A19 H

Where '-' appears to be high impedance (logic probe is silent)

[Link to Original Thread / Board #3]

Here's what I know so far:

- Motherboard type 64KB-256KB

- Known good CPU inserted

- Known good RAM populated in Bank0, other banks unpopulated

- RDR Doesn't boot up, no beep, LPT says "00" and nothing more

- Booting with known good BIOS, no beep, no video

- Verified power supply

- Verified 4.77 MHz clock

- No pulses on pin 13 of the 8253 chip

Performed The 'ground I/O CH RDY' Procedure, this is what I see:

8088's READY (22) and RESET (21) pins are LOW

A0 H

A1 H

A2 H

A3 H

A4 H

A5 H

A6 H

A7 H

A8 H

A9 -

A10 L

A11 L

A12 H

A13 -

A14 -

A15 -

A16 H

A17 H

A18 H

A19 H

Where '-' appears to be high impedance (logic probe is silent)

Last edited: