modem7

10k Member

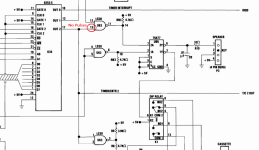

If we just look at A13 (for the procedure), crudely:It is starting to feel like U9 is bad isn't it

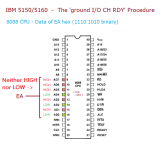

1. 8088 takes its A13 pin to HIGH, and sets its three status pins to indicate a memory read operation.

2. The 8288, seeing a memory read operation, knows that the 8088 has outputted an address, and accordingly, the 8288 pulses its ALE pin.

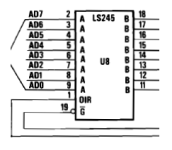

3. That positive going pulse causes U9 to sample its pin 7 (connected to the 8088's A13 pin) and put that into a latch within itself.

4. With U9-1 being LOW, that gets U9 to output the aforementioned latch output out onto pin 6.

But I can put most of that aside.

If I look at the datasheet for a 74LS373, pin 1 being low takes the outputs out of high impedance state - the outputs should be either HIGH or LOW.

You are not seeing that for the output corresponding to A13.

U9 at fault, or affected by something on the address bus ?