misterblack

Experienced Member

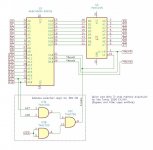

I'm game to try. With the LS151 reconnected I can deselect the 384-512k bank from the SRAM... although it seemed the 151 introduced some timing errors that caused other issues. But I could disable that bank while the system was running and if it continues to just magically work that would be telling.

Hmm had you scoped the OE pins on the motherboard DRAM while running a RAM check on the 384-512k pages? (Which SRAM was also in that space.) That should be quite telling and tell us right away if both RAM chips are driving the bus.

Edit: Another thought -- would just removing the extra 128k of RAM turn the EX/HX into a 128k system? I wonder if it works that way. I'm curious now too! That might be the way to go if we find there is a BUS conflict... Easier if someone wants to use a single chip SRAM board without deselecting. I will test this out tonight .. my EX has zero RF shields anymore (is anyone surprised?!?) so it's easy to yank RAM chips.

Hmm had you scoped the OE pins on the motherboard DRAM while running a RAM check on the 384-512k pages? (Which SRAM was also in that space.) That should be quite telling and tell us right away if both RAM chips are driving the bus.

Edit: Another thought -- would just removing the extra 128k of RAM turn the EX/HX into a 128k system? I wonder if it works that way. I'm curious now too! That might be the way to go if we find there is a BUS conflict... Easier if someone wants to use a single chip SRAM board without deselecting. I will test this out tonight .. my EX has zero RF shields anymore (is anyone surprised?!?) so it's easy to yank RAM chips.

Last edited: