found another bad socket and replaced it.

here's what I can report:

test 1/post 24:

CPU card in.

C3 U10-12 low

HAD U14-6 low

NOP U13-4 low

LAD U12-8 low

test 2/post 28:

all data bus LEDs on. 7405 outputs U6-4, U6-10, U6-8, U4-12, U4-8, U3-12, U3-10, U3-8 are high.

test 3/post 48:

all switches closed/down, all data leds on.

test 4/post 49:

sw0-15 all open/on/up, U12 removed.

C3 U10-12 low

HAD U14-6 low (U4-11, U4-9, U3-13, U3-9, U1-13, U1-11, U1-9 all low)

NOOP U13-4 low

switch 0-6 toggles the data bus LEDs on/off.

test 5/post 54:

U12 in, U14 removed, all switches open/up/on.

LAD U12-8 low

C3 U10-12 low PULSING

NOOP U13-4 low

switches 8-15 toggle data LEDS 0-7 on/off.

other than C3 pulsing low, I think these are all the expected results.

here's what I can report:

test 1/post 24:

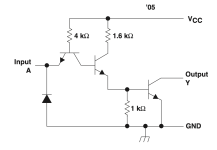

Ok, if you look at the schematics for the front panel you should notice that all of the 7405 gates (including the address/data switches) are divided into four (4) groups driven by the signals LAD, HAD, C3 and NOOP.

The four groups are connected to a common bus going to socket U2.

A 7405 gate is an open collector inverter. As such, they do not have a pull-up to 5V. The pulls-up resistors are all on the CPU board (after U2).

First thing, after a power-up, STOP and RESET; can you measure the state of signals LAD, HAD, C3 and NOOP using your logic probe.

They should all be LOW with no pulses on them.

A LOW input to the 7405 gates should make the outputs all float. If all of the address/data switches are CLOSED, your logic probe should read all HIGH signals on socket U2.

That is the first test.

Let me know what you obtain.

Dave

CPU card in.

C3 U10-12 low

HAD U14-6 low

NOP U13-4 low

LAD U12-8 low

test 2/post 28:

Excellent.

So all of these signals LOW means that we are feeing a LOW into all of the 7405 inverters and (therefore) the output from all of the 7405 inverters should all be open circuit.

With all of the address/data switches CLOSED - this should mean that the signals on the U2 connector should all be HIGH (due to the action of the pull-up resistors on the CPU card).

Also, with all of the address/data switches CLOSED, the outputs from all of the 7405 inverter gates should also be HIGH (due to the action of the pull-up resistors on the CPU card 'feeding back' through the CLOSED address/data switches). In addition, the outputs from the 7405 inverters that do not go via a switch should also be HIGH.

Is this all correct?

Dave

all data bus LEDs on. 7405 outputs U6-4, U6-10, U6-8, U4-12, U4-8, U3-12, U3-10, U3-8 are high.

test 3/post 48:

Excellent.

With switches SA0 through SA15 CLOSED. Are all the data bus LEDs illuminated on the front panel?

Dave

all switches closed/down, all data leds on.

test 4/post 49:

If the above is correct, here is how I would proceed.

Power ON. HALT and RESET.

Set all of the switches SA0 through SA15 to OPEN. The data bus LEDs should all be ON.

Power off and remove IC U12 - observing the correct polarity of the IC within the socket for subsequent installation.

I am 'hoping' that this will cause the LAD signal to float HIGH (due to the action of the weak pull-up resistors on the inputs of the connected 7405 gates).

Power ON. HALT and RESET.

Test signals HAD, C3 and NOOP again (with your logic probe). I am hoping these three signals should all be LOW. If not, report and stop.

In theory - with the 7405 inputs HIGH (due to the signal LAD being pulled HIGH due to the internal pull-up resistors) the outputs from these 7405 gates connected to LAD should all be LOW.

By CLOSING switch SA0 - this should cause the data bus LED D0 to extinguish. The other data bus LEDs should remain illuminated.

By OPENING switch SA0 - data bus LED D0 should illuminate once again.

Repeat this test for SA1 through SA7 in turn (CLOSE followed by OPEN) and data bus LEDs D1 through D7 (respectively) should extinguish and illuminate.

If this is the case, power OFF and re-install IC U12 in the correct orientation (as found). Check for any bent pins on IC U12 after installation.

Report the results.

Dave

sw0-15 all open/on/up, U12 removed.

C3 U10-12 low

HAD U14-6 low (U4-11, U4-9, U3-13, U3-9, U1-13, U1-11, U1-9 all low)

NOOP U13-4 low

switch 0-6 toggles the data bus LEDs on/off.

test 5/post 54:

Excellent!

So, re-install IC U12 (if you haven't already) and repeat the same hassle (!) by removing IC U14 driving the HAD signal.

Make sure switches SA0 through SA15 are all OPEN.

Again, STOP and RESET.

Check that signals LAD, C3 and NOOP are all LOW.

Repeat the same process using switches SA8 through SA15.

SA8 should drive data bus LED D0 and SA15 should drive data bus LED D7 (with all of the inbetween SAn switches driving the other data bus LEDs in the same way).

Dave

U12 in, U14 removed, all switches open/up/on.

LAD U12-8 low

C3 U10-12 low PULSING

NOOP U13-4 low

switches 8-15 toggle data LEDS 0-7 on/off.

other than C3 pulsing low, I think these are all the expected results.