I understand the frustration, this sort of thing is not really easy - despite what the instructions might imply. And to do this while learning (about Z80 ASM and CP/M) is even harder. If I had a virtual machine to match your hardware, I could probably be of more help. I'm strapped for spare time right now, though.

another area to pay attention to, when creating the BIOS3 code, is the DPH and associated structures. There are some subtle differences and new structures which need to be carefully handled.

I'l try to find some time this weekend to take a closer look at your BIOS code and see if I can help by inspection. If you've got something to document your hardware, that might be nice. either "programmer notes" or a schematic.

You sir are a star. :D

I don't have a single schematic for the design - the schematics are quite modular. However, here's a summary of features that should help:

The SBC has a flexible MMU, which splits the Z80's 64KB memory space into 4 16KB 'Areas', each able to be independently mapped to any 16KB Bank in the 256K available physical memory (128KB SRAM in lower half, 128KB EEPROM in upper half.) With the addition of a CompactFlash card, the SBC has permanent storage allowing it to run CP/M 2.2. It uses an ATmega328 microcontroller to enhance its IO potential:

- Z80 microprocessor at 2, 4 or 8 MHz clockspeed, software-selectable

- 128K SRAM (00000h-1FFFFh)

- 128K ROM (20000h-3FFFFh)

- MMU provides access to 256KB physical memory in 16x16KB Banks, mappable to the Z80 in any arrangement as 4x16KB Areas

- Z80 SIO/2 providing two serial interfaces, with interrupt-driven Rx channels to prevent unnecessary polling of the Rx buffer when not in use

- CompactFlash adapter with 64MB CF card providing 8x 8MB drives for file storage

- OS - Custom ROM monitor providing NASCOM BASIC, memory and Intel HEX file input utilities & CP/M 2.2

- I2C bus via Support Module - currently supports Real Time Clock module

- Fully-expandable interrupt system

- Z80 CTC for clock/timer functions and user-programmable triggerable interrupts

- Z80 PIO for 2-channel parallel IO

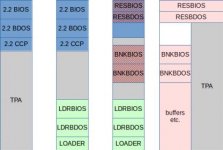

Power-up Memory Map:

- Area 0 - 0000-3FFF ROM (Bank 0F - DMI monitor)

- Area 1 - 4000-7FFF RAM (Bank 01)

- Area 2 - 8000-BFFF RAM (Bank 02)

- Area 3 - C000-FFFF RAM (Bank 03)

Memory Map in CP/M mode:

- Area 0 - Bank 0 (SRAM)

- Area 1 - Bank 1 (SRAM)

- Area 2 - Bank 2 (SRAM)

- Area 3 - Bank 3 (SRAM)

- 0000-0100 Scratch storage & interrupt vectors

- 0100-D800 TPA

- D800-E5FF CP/M

- E600-FFFF BIOS

- 00-07 SIO/2 dual-port serial interface

- 08-0F Reserved for PSG

- 10-17 CompactFlash interface

- 18-1F CTC 4-channel programmable clock/timer

- 20-27 PIO 2-channel parallel I/O

- 28-2F Unused

- 30-37 Unused

- 38-3F Memory Management Unit

The MMU is controlled via an

Code:

OUT ($38),n- B7 - low = MMU active, high = MMU inactive

- B6 - not used

- B5, B4 = Area select

- B3-B0 = Bank select

Code:

OUT ($38),02Also, I've attached the current CBIOS for CP/M 2.2 - this works with my SBC to allow CP/M 2.2 to run without problems.

Attachment: View attachment cbios64.zip