This looks interesting but I'm skeptical about their application note. If RESET (pin 6) is undefined when the voltage is below the reset threshold, then assume "undefined" could mean it's in the wrong state. So, with the voltage low but not zero, the proper state of RESET would be high (actually open collector is off), but if RESET were improperly low (open collector pulling down, then Q1 would be saturated and pull the "System RESET_bar" signal high in the not reset state. I think once the voltage detector produces the wrong state there is not a way to correct it.

I'm not advocating to change your design :-}. But I think that your interpretation regarding the behavior of the TL77xxA is incorrect in two respects -- and at this stage experimental evidence is lacking but ...

(FWIW, perhaps you are looking at the older data sheet from March 2012 "Supply Voltage Range: 2 V to 6 V" which are the not-A parts, and I'm looking at the newer data sheet from September 2016 "supply voltage range of 3.5 V to 18 V" which are the superseding A parts?)

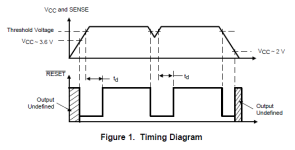

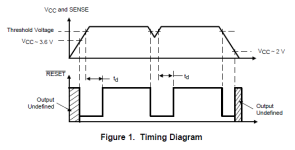

First, IMO Figure 1 is a bit obtuse, designed for marketing more than engineering:

Note that the label on the upper ordinate conflates Vcc with Sense. IMO their point is that the IC requires a minimum of 3.6v in order to operate properly (so stated in the prose); it's necessarily the case that the output signals can't exceed applied Vcc and as the table in 6.5 identifies that Voh MIN is Vcc-1.5v this means that it's simply not possible to achieve Voh as the "high" logical value that they define (>3.5v) when Vcc < ~3.6v.

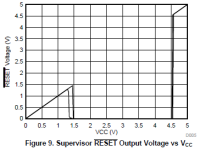

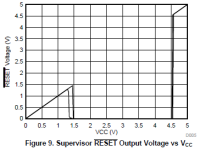

The lower ordinate is a logic-value (in their MIN/MAX terms) rather than a voltage -- and if graphed as a voltage it necessarily is constrained on the high-side as a ramp. See Figure 9, which is an honest plot of voltage, rather than logic value:

So "undefined" means that Vol (MAX 0.4v) isn't being met either; the output exceeds the logic-zero max and is less than the logic-one min. It's still a quite well-known voltage; it's just an analog value that can't be interpreted digitally using their MIN/MAX definitions. There is no "state" here.

Note that while the ~RESIN input uses TTL logic levels, the pair of RESET outputs use a different definition of logic levels. The pair of RESET outputs operate in analog-mode below ~3.6v, and in digital-mode above that Vcc. And digital-mode is IAW their definitions of logic-zero and logic-one.

We need to keep in mind that these circuits aren't being supplied by a nice meets-spec Vcc while only SENSE is fluctuating ... which at least for me makes this all a bit of a head-scratcher!

Second, I don't agree that the presence of hysteresis operating around the Vt (4.55v) has any bearing on the behavior of the device when Vcc < 3.6v. I don't think that there's any "latching" going on. Furthermore I can't imagine a common part like this being designed and sold to behave as badly as you describe :-}! It would _not_ be fit-for-purpose, IMO. What sort of product designer would contemplate using a part that was in effect metastable at power-on, ending up in an arbitrary latched state precluding further use as a supply voltage supervisor?

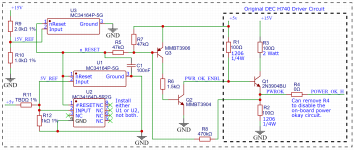

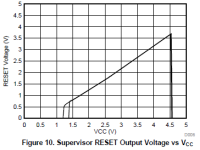

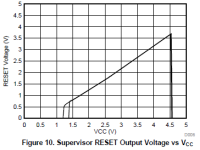

It seems to me that the point to the PNP-follower is to ensure that the (output) System ~RESET signal -- based on the RESET curve in Figure 10:

-- conforms to TTL(ish) logic levels in the low-Vcc setting by ensuring/letting the output System ~RESET rise directly with Vcc (thus "as one/true as it can be", removing the low-Vcc "notch" in Figure 10) until RESET "snaps over" to ~0V (logical zero/false) and Q1 is driven into conduction, the objective being to avoid the logical No Man's Land that the TL77xxA can't avoid on its own under low-Vcc conditions. System ~RESET simply "floats" upwards based on rising Vcc and the characteristics of the input of the downstream device(s) until Q1 snaps into conduction. With full Vcc achieved, Q1 then operates as a simple inverter (and all is well in the world :-}).

My guess is that the TL77xx designers felt that the cost of incorporating the additional circuitry on-chip outweighed customer-value in common use-cases (MCU ~RESET, which are typ. more forgiving inputs than strict/simple TTL)? However they illustrated two designs for potential use in situations with more exacting requirements, e.g. "strict TTL" -- which is the use-case that concerns us here.

Perhaps I am completely misunderstanding the design and behavior of the TL77xxA and the PNP-follower, in which case please do set me straight ... because I'm "not with you" as yet :-}.