kiwisincebirth

Member

- Joined

- Jan 28, 2025

- Messages

- 37

I have been looking into the Model 3 and its video generation, and specifically its ability to De-Glitch. During this research I came across this article

Double-wide Bug

http://48k.ca/bug32.html

George Phillips, October 5, 2009, george -at- 48k.ca

It talks about the an issue in the Model 3 where --- "If the display is in double-wide mode (32 x 16 characters),

And the processor reads or writes video memory, Near the time the video circuitry is reading video memory,

Then the next RAM access by the processor will be corrupted." --- but offers no solution.

So is this (the following) the reason ? First off I don't think it is related to 32 char mode specifically, here are my thoughts

First lets go back to whats happening, memory access is being corrupted by Video Ram (I will abbreviate to VRAM) , how does this occur. The following is the buffer which buffers VRAM onto the Data bus. The important point is the controls are by VRD* and VWR*. Where do they come from.

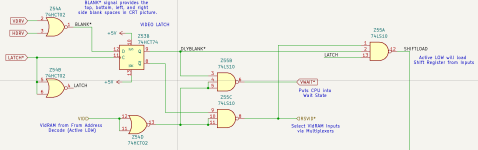

These come from one of the multiplexers that selects the address/control lines (inputs) to the VRAM. You can see the VRD* and VWR* signals here, the top inputs are from the video circuitry (note how the VWR and VRD are selected as HI, basically disabling the above buffer), and the bottom input come from the CPU. Note the S line (not shown) comes from RSVID*

RSVID* comes from the below logic, in summary it takes two inputs, VID* - (address decoder for VRAM), and PBLANK* (is Video currently in one of the blanking intervals)

and produces 2 opposing outputs

This is where it gets interesting.

If you read the The gate on the right (below) is an OR gate with negating inputs - The CLOCKP is multiplexed from one of 2 signals depending on RSVID*

... OK? So what does this mean ...

This means that is CPU currently has control of VRAM the new status of VID* (VRAM address decoder) will not be clocked into the JK flip flop until the next LATCH, which happens when the raster needs to read the next VRAM byte - This could take some time ...

So after CPU has successfully done its VRAM access, The CPU A0-A9, RD* WR* signals will remain connected to VRAM, and of course this is without any address decoding! VID* is no longer asserted,... well that is until the raster needs to read the next VRAM byte. This is why the problem is only observed in 32 Character mode, its simply a case of the VRAM being exposed to the bus for longer.

Simple Solution: Get rid of CLOCKP (and the circuit above), just use CLOCK. In this case what is the purpose of the JK FLIP flop in the first place ?

Make Sense?

Double-wide Bug

http://48k.ca/bug32.html

George Phillips, October 5, 2009, george -at- 48k.ca

It talks about the an issue in the Model 3 where --- "If the display is in double-wide mode (32 x 16 characters),

And the processor reads or writes video memory, Near the time the video circuitry is reading video memory,

Then the next RAM access by the processor will be corrupted." --- but offers no solution.

So is this (the following) the reason ? First off I don't think it is related to 32 char mode specifically, here are my thoughts

First lets go back to whats happening, memory access is being corrupted by Video Ram (I will abbreviate to VRAM) , how does this occur. The following is the buffer which buffers VRAM onto the Data bus. The important point is the controls are by VRD* and VWR*. Where do they come from.

These come from one of the multiplexers that selects the address/control lines (inputs) to the VRAM. You can see the VRD* and VWR* signals here, the top inputs are from the video circuitry (note how the VWR and VRD are selected as HI, basically disabling the above buffer), and the bottom input come from the CPU. Note the S line (not shown) comes from RSVID*

RSVID* comes from the below logic, in summary it takes two inputs, VID* - (address decoder for VRAM), and PBLANK* (is Video currently in one of the blanking intervals)

and produces 2 opposing outputs

- PWAIT* - put the CPU into a wait state basically since the VRAM is needed by Video generation

- RSVID* - buffer the VRAM to the CPU, turn video RAM over to CPU BUS.

- LATCH - is the signal that loads the VRAM buffers (from RAM before the bits are shifted out)

- CLOCKP - So what is CLOCKP ?

This is where it gets interesting.

If you read the The gate on the right (below) is an OR gate with negating inputs - The CLOCKP is multiplexed from one of 2 signals depending on RSVID*

- if RSVID* is inactive - CPU doesn't have access - (bottom half) then CLOCK. This makes sense the RD / WR signals could change with any given clock pulse. Noting this is the base clock not the cpu clock. But regardless of the CPU asserts a VRAM address onto the Address bus the selection logic (above) needs to know about it.

- If RSVID* is active - CPU does have access) - (top half) then clock with the LATCH signal ???

... OK? So what does this mean ...

This means that is CPU currently has control of VRAM the new status of VID* (VRAM address decoder) will not be clocked into the JK flip flop until the next LATCH, which happens when the raster needs to read the next VRAM byte - This could take some time ...

So after CPU has successfully done its VRAM access, The CPU A0-A9, RD* WR* signals will remain connected to VRAM, and of course this is without any address decoding! VID* is no longer asserted,... well that is until the raster needs to read the next VRAM byte. This is why the problem is only observed in 32 Character mode, its simply a case of the VRAM being exposed to the bus for longer.

Simple Solution: Get rid of CLOCKP (and the circuit above), just use CLOCK. In this case what is the purpose of the JK FLIP flop in the first place ?

Make Sense?