dmemphis

Experienced Member

I started this one last year but can't find the thread. I'm back on it now

tired of having this nice machine sitting here in two pieces in a bad way.

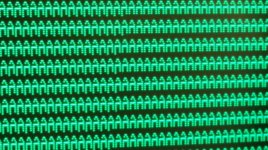

This is the symptom - the first pixel of every character clocked out to video is dark.

http://imgur.com/PIhmEPy

Its dead consistent from power up to power up.

D's and Y's look normal I think because they are narrow and centered- their first dot is blank anyway.

I swapped the character ROM and the display controller ICs - no change at all.

I checked that the data path between character ROM U19 to PLD U17- its good; there

are pulses on D0 at both ends (How I hoped this signal was the problem I expected a bad

ROM driver or open trace but NO!) (I scoped ON the pin at the PLD, so I know the ROM bits get there)

I looked at all the signals around U17, U19, U16, U12, U14,U15- they look healthy.

I'd like to swap in replacements for U17, U9, and U8 but this is the only Gate Array board

I have.

Know of any failure modes that might obscure the first dot of every character clock out?

I mostly suspect a weird failure in U17 as it does the shift of the ROM byte and could be doing

something wrong with the first bit. I'd need a spare U17 to check that with.

Or it could be the PLA is being told to do something wrong, ie: its erroneously

putting out a non existent graphics bit at that time instead of the ROM bit. I don't

fully understand the switching and mixing of the graphics data with the character data.

I'd hate to think its a really hairy timing thing that I'll have to measure all the signals in detail...

Thanks in advance TRS-80 commandos.

tired of having this nice machine sitting here in two pieces in a bad way.

This is the symptom - the first pixel of every character clocked out to video is dark.

http://imgur.com/PIhmEPy

Its dead consistent from power up to power up.

D's and Y's look normal I think because they are narrow and centered- their first dot is blank anyway.

I swapped the character ROM and the display controller ICs - no change at all.

I checked that the data path between character ROM U19 to PLD U17- its good; there

are pulses on D0 at both ends (How I hoped this signal was the problem I expected a bad

ROM driver or open trace but NO!) (I scoped ON the pin at the PLD, so I know the ROM bits get there)

I looked at all the signals around U17, U19, U16, U12, U14,U15- they look healthy.

I'd like to swap in replacements for U17, U9, and U8 but this is the only Gate Array board

I have.

Know of any failure modes that might obscure the first dot of every character clock out?

I mostly suspect a weird failure in U17 as it does the shift of the ROM byte and could be doing

something wrong with the first bit. I'd need a spare U17 to check that with.

Or it could be the PLA is being told to do something wrong, ie: its erroneously

putting out a non existent graphics bit at that time instead of the ROM bit. I don't

fully understand the switching and mixing of the graphics data with the character data.

I'd hate to think its a really hairy timing thing that I'll have to measure all the signals in detail...

Thanks in advance TRS-80 commandos.