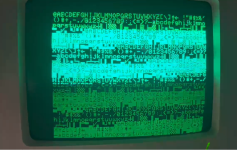

Think about it.

The original ROM is 2K.

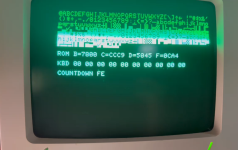

My PETTESTER is 2K.

The 27512 EPROM is 64K.

That means the 27512 EPROM can hold 32 off 2K ROM images.

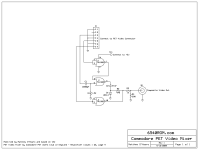

If you look at the schematic for the adapter, you should observe that the extra address lines (A11 through A15) are individually pulled HIGH via a resistor.

This means that the default address of the start of the 2K ROM image within the 27512 EPROM is 1111_1XXX_XXXX_XXXX = $F800.

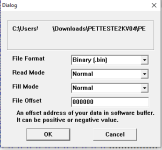

You set your EPROM programmer up to tell it that it is going to program a 27512 device - but (before you load the PETTESTER image) you also have to tell it there is an offset of F800 (hex) that the EPROM programmer has to apply BEFORE loading the binary image.

The EPROM programmer should, then, load the 2K PETTESTER binary image into the LAST 2K of the 27512 EPROM.

When you plug this into the adapter, address $F800 in the 27512 EPROM will magically become address $0000 relative to the adapter chip select (which is $E000) and everything should be good with the world!

Alternatively, and this will avoid all of this palaver, you could connect the unused address lines A11 through A15 (on the adapter board) to 0V instead, thus making the default 27512 offset 0000_0XXX_XXXX_XXX or $0000.

I hope this makes sense.

Dave