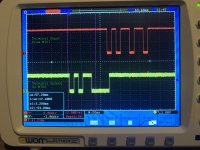

More stuff is running now. Adjusted the timing of STROBE FIELD 0 (by adjusting the screw on the M360 delay in slot C17) so the pulse ends at about the peak of the data pulse out of the sense amplifiers. Now the data read from core memory is sampled at the point where the signal is strongest. BTW, memory cycles are being initiated by flipping switches on the front panel because I can't reliably run programs yet.

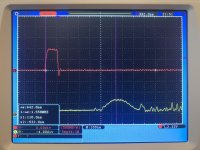

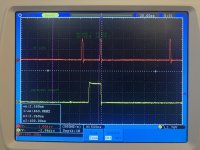

Next problem: MB09 was always zero after the first read. After writing a one to bit 09, the data pulse was visible at the output of the sense amplifier. The top trace is I think MEM START and bottom is pin 10 of the sense amplifier corresponding to bit 09.

However, on the second read there was no data pulse! Problem was the sense amp strobe enable wasn't working and data wasn't being latched on the G020 card. But the G020 card had a yellow sticky dot so it was tested in the FlipChip tester. Turns out I apparently forgot to copy the updated G020v2.TST to the SD card in the tester and didn't fully test the board. Swapped in a good one from the spares kit since I don't have a spare MC1540 amplifier chip. Confirmed that G020v2.TST does fail the bad G020 that was removed.

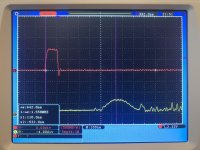

Tried to run a "Hello World" program but discovered memory was not reliable around location 200. Put that on the to-do list. Higher pages seem reliable, so put Hello World at 7200. Now, something is crazy: monitoring the serial output on the scope, the string pointer starts at the second character and each character value is one more than the value it should be (so: instead of "Hello..." it was "Ifmmp..."). Happy I can see some characters coming out of the M707 Teletype Transmitter. Even though it's not quite correct, at least a lot is working for this to happen! By single stepping it's obvious that the TAD instruction is computing the proper value plus 1. In high memory the following program was used for debugging:

7400 1202 TAD 7402

7401 5200 JMP 7400

7402 0000

Started by tracing data through the paths on the M220, looking first at the LSB. It was properly selecting MEM11 and AC11 for the adder inputs. The AOI gates send one's compliment of data to the SN7482 2-bit adder chip. The adder output and AC11 are of course toggling like crazy. After a few minutes of drawing logic diagrams and following examples with pen and paper it's apparent that taking one's compliment of adder data inputs and inverting the carry input produces the one's complement of the sum. (This one's compliment of the sum is inverted again by another AOI gate to become the REG BUS value which is saved in the AC. The bit 11 adder carry input, "CARRY INSERT" was low at the rising edge of the AC LOAD pulse. This isn't right, because all inputs to the adder should be inverted data. Traced that back to the M160 AOI gates in slot A12. Checked all inputs and confirmed the AOI output should be "1", but the output is "0", which injects a carry into the adder which adds one when it shouldn't. This M160 has a yellow sticky dot so it was tested in the tester! Put the M160 back in the tester and it passes! Can't be! It fails in the machine but passes in the tester. Carefully studied the test program steps that test pins M1 N1 P1 and realized there's a bug. The test vectors skipped over the case of the bad input that exists on this board. Modified M160.TST with a simple fix and now the bad M160 fails in the tester, and a good M160 from the spares kit passes in the tester. Swapped in the good M160 into slot A12, and now the TAD instruction works properly. It appears to have been a bad SN7460 AOI expander gate on the M160.

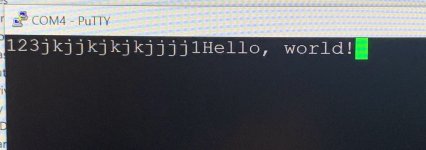

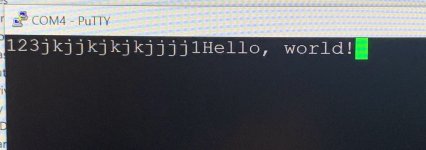

Connected a USB to CMOS serial cable to the M707 TTY Transmitter output, fired up Putty and set baud rate to 110 bps. Ran the Hello World program and...

(The 123jkjj... are from me testing the serial cable with a wired loopback.)

Next step, test the serial receiver using a serial echo program.

Also, there's still the issue with slightly forgetful low memory pages. And there was an older issue with memory bit 04 that would occasionally be one when it shouldn't. maybe that's related to the low memory page flakeyness... need to investigate.