gwiley

Experienced Member

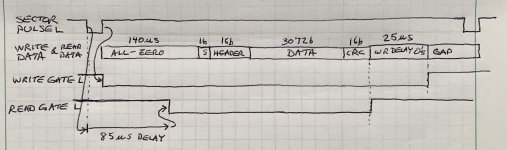

Is this RK05 test interface operating, or is there documentation in a form where it could be cloned? Does it read and write or is the purpose primarily intended to duplicate functionality of the original RK05 exerciser?I have built my RK05 test interface and currently writing software for it.

Until so far it is doing what I want...

View attachment 1039584

To rigorously test the RK05 emulator I was planning to flip the emulator signals so the emulator could be a tester. I think @PDP11GY has done this too.

Considering the following functionality but maybe it already exists?

Select drive always

Unselect drive

Seek to cylinder

Seek loop list of cylinders

Read sector

Loop read sector

Write sector

Loop write sector

Read track

Loop read track

Set mode: RK8E, RK11D or E

Display the mode & status

Display the sector read data

Copy disk to microSD