leeb

Veteran Member

Okay... see if you can follow me here.

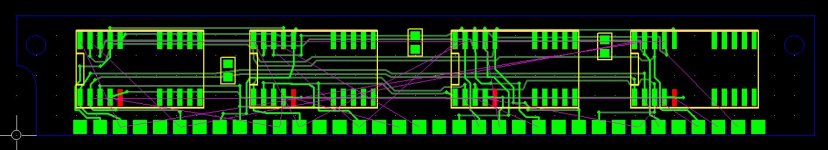

I am attempting to repli-create the 35-pin 1Mb(256kx4x8 ) RAMS for my 2810s and similar panasonic laptops...

and I have been having trouble with routing, pretty much everything!

So... I have 4 chips on each side, and unlike the original RAMs (which were rung out for this purpose), I am 'adjusting' things.

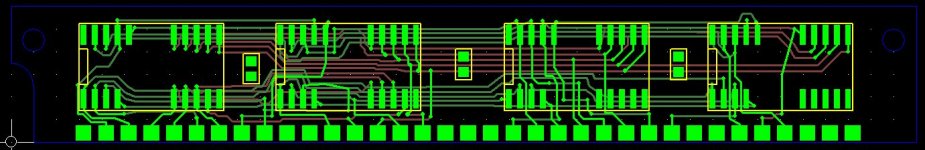

I am not following the normal routing of data0-7 to pin(d0-7), but have 'mixed' them to get shorter/less complicated traces, which has kept me down to 3 layers so far...

But, what about the ADDRESS lines (A0-A8.. total of 9 )?

Being as they are dynamic RAMs, would having the addresses 'scrambled' by not following the normal binary pattern cause refresh issues?

A total of 8 lines gives 0-255... so no matter what order they are in, there will still be only 255 possible combinations, just not 'linear'.

Any thoughts? :twisted:

Uh oh... the 666th post!

I am attempting to repli-create the 35-pin 1Mb(256kx4x8 ) RAMS for my 2810s and similar panasonic laptops...

and I have been having trouble with routing, pretty much everything!

So... I have 4 chips on each side, and unlike the original RAMs (which were rung out for this purpose), I am 'adjusting' things.

I am not following the normal routing of data0-7 to pin(d0-7), but have 'mixed' them to get shorter/less complicated traces, which has kept me down to 3 layers so far...

But, what about the ADDRESS lines (A0-A8.. total of 9 )?

Being as they are dynamic RAMs, would having the addresses 'scrambled' by not following the normal binary pattern cause refresh issues?

A total of 8 lines gives 0-255... so no matter what order they are in, there will still be only 255 possible combinations, just not 'linear'.

Any thoughts? :twisted:

Uh oh... the 666th post!

Last edited: