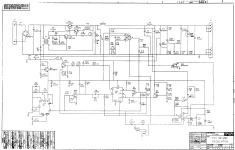

I will have to go through in detail, but at a glance, this is what I am seeing:

- D1/F1/C1 provide fused rectified unregulated DC (voltage depends on what is hooked to J1).

- Q4 provides an unregulated 12V to power the rest of the regulator

-E1, as you said, is an oscillator providing a pulse train to the rest of the circuit, used for PWM and a negative voltage reference.

-D17, D25, C5 provide a negative voltage rail for the LM301's

- E2 is a PWM circuit, diiscussed in pieces below:

- The output pin 3 drives the primary of T1, producing current on the secondary, which is rectified to activate Q3.

- Q1 and Q2 are parallel power transistors acting as a single NPN transistor the differential choke provides a reactive ballast, canceling the small differences due to mismatch without the constant loss of ballast resistors.

- Q3 and Q1+Q2 form a Sziklai pair pass element, driving L1 + L2, which form the output inductor and C16 stores the passed charge, smoothing the output voltage.

- D20 and D21 implement overvoltage protection. D20 crowbars the output to ground, and D21 inhibits the PWM output of E2.

- Here's how I think the PWM works, with some simplifications. The timing of the various events below will be voltage dependent, and depending on charge rates, some steps could be flipped.

- LM301 E4 provides a negative feedback signal with DC offset, applied to the E3 pin 5 Control Input, and to C6 at the Trigger input (E3 pin 2)

- With E1 pin 3 output low, Q6 is off, and the Trigger rests at the offset error level.

- When E1 pin 3 output goes high, Q6 is on, and the low side of C6 is pulled close to ground, activating the trigger of E2, bringing E2 output pin 3 high, turning off the DISCHARGE trnasistor.

- Once DISCHARGE is off, Q8,R23, D14, D15, R24 form a current source that charges C10 until the voltage matches the feedback output of E4, at which point E2 output resets and C10 is discharged. Larger error signals mean lower control voltage, and quicker threshold, so shorter PWM pulses.

- The LM301 E3 is a comparator sensing the return current. An overcurrent forces the output high, holding the E2 (PWM) 555 timer in the RESET state via Q7, and grounding the reference voltage to the E4 error amplifier via Q9, minimizing the pulse width.

- There are a few other variables such as the CTL signal also charges C6, so the triggered state is released sooner for low output voltages and later for high output voltages. This could also stretch or shrink the duty cycle, depending on relative charge rates of C10 and C6. Or this could not kick in until E3 grounds the postive input of E4, which could then potentially delay the release of the trigger long enough to completely inhibit the pulse. A scope would be helpful.