Twospruces

Veteran Member

It has been some effort, but I am really enjoying the outcome.

I have what I would call a pretty unique CP/M system here.

Starting with a stock TRS-80 Model 100, I have....

* firstly developed a plug and play SRAM card that enables 64k RAM mode + a 3.5MB ramdisk - REXCPM

* supported Mr. Avery in the development of M100 CP/M - a port of CP/M 2.2 intended to leverage said REXCPM

(all of this is documented at the M100 Wiki: http://bitchin100.com/wiki/index.php?title=REXCPM)

so, to this point, what you get is an 80C85 based CP/M rig, on a 40x8 LCD. Nice!

Then, taking it a bit further, recall some earlier discussion about the NSC800 CPU - aka Z80 in 8085 clothing.

* I now have a small adapter board that supports running the NSC800 in the M100. 2.5MHZ Z80.

* (and it turns out you need to change the embedded ROM a bit to handle certain changes to the interrupts)

* I found a way to drive Tx TTL serial data out the somewhat underused BCR port as well, freeing up the sole RS-232 port for other uses. (my "BCR Hack").

And then lastly, to expand the video capabilities

* I have a version of the Geoff VT-100 terminal, modified just slightly to make it work better with M100. This converts serial TTL console to VGA.

End result-

A TRS-80 Model 100 running "Z80" with an external 80x24 LCD and a fast internal SRAM disk for CP/M 2.2.

Pics:

Here is the view of the main board. You can see my NSC800 adapter and the adapter for a revised main ROM.

Closeup of the NSC800 adapter:

Closeup of the main ROM adapter with the slightly revised Microsoft main ROM.

And finally, the complete system, which happens to be running Turbo Pascal 3.0. You can also see the VT100 adapter converting console serial data to VGA.

So far it is running flawlessly. Some of you may recall, as pointed out in the Microsystems Sept 84 article on making NSC800 adapters for 8085, that the NSC800 has a short opcode fetch cycle. In the M100, no wait state is needed; everything seems fast enough to keep up.

I have no problems running whatever CP/M software I like it seems.

In truth, the system works with either the stock 80C85 or the NSC800. I guess there is only a minor advantage in having the Z80 compatible under the hood; much of the software is 8080. Still it was a challenge to do, and I'm happy with the result.

REXCPM and M100 CP/M are available. I'm working on an NSC800 adapter that is good enough to share or offer as a kit. I've posted an interim schematic and layout at the same wiki mentioned above as well.

None of this is particularly hard to do. The biggest part of the conversion is the removal of the 80C85 and the addition of a socket.

Cheers, comments welcome.

I have what I would call a pretty unique CP/M system here.

Starting with a stock TRS-80 Model 100, I have....

* firstly developed a plug and play SRAM card that enables 64k RAM mode + a 3.5MB ramdisk - REXCPM

* supported Mr. Avery in the development of M100 CP/M - a port of CP/M 2.2 intended to leverage said REXCPM

(all of this is documented at the M100 Wiki: http://bitchin100.com/wiki/index.php?title=REXCPM)

so, to this point, what you get is an 80C85 based CP/M rig, on a 40x8 LCD. Nice!

Then, taking it a bit further, recall some earlier discussion about the NSC800 CPU - aka Z80 in 8085 clothing.

* I now have a small adapter board that supports running the NSC800 in the M100. 2.5MHZ Z80.

* (and it turns out you need to change the embedded ROM a bit to handle certain changes to the interrupts)

* I found a way to drive Tx TTL serial data out the somewhat underused BCR port as well, freeing up the sole RS-232 port for other uses. (my "BCR Hack").

And then lastly, to expand the video capabilities

* I have a version of the Geoff VT-100 terminal, modified just slightly to make it work better with M100. This converts serial TTL console to VGA.

End result-

A TRS-80 Model 100 running "Z80" with an external 80x24 LCD and a fast internal SRAM disk for CP/M 2.2.

Pics:

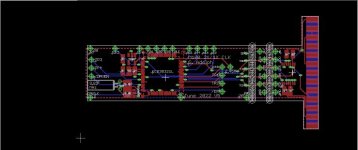

Here is the view of the main board. You can see my NSC800 adapter and the adapter for a revised main ROM.

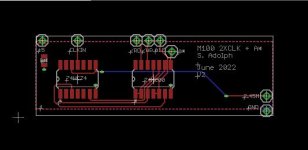

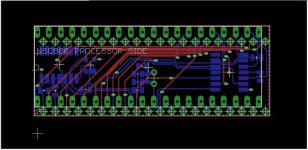

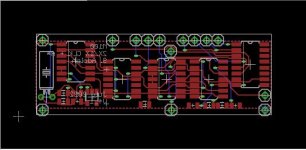

Closeup of the NSC800 adapter:

Closeup of the main ROM adapter with the slightly revised Microsoft main ROM.

And finally, the complete system, which happens to be running Turbo Pascal 3.0. You can also see the VT100 adapter converting console serial data to VGA.

So far it is running flawlessly. Some of you may recall, as pointed out in the Microsystems Sept 84 article on making NSC800 adapters for 8085, that the NSC800 has a short opcode fetch cycle. In the M100, no wait state is needed; everything seems fast enough to keep up.

I have no problems running whatever CP/M software I like it seems.

In truth, the system works with either the stock 80C85 or the NSC800. I guess there is only a minor advantage in having the Z80 compatible under the hood; much of the software is 8080. Still it was a challenge to do, and I'm happy with the result.

REXCPM and M100 CP/M are available. I'm working on an NSC800 adapter that is good enough to share or offer as a kit. I've posted an interim schematic and layout at the same wiki mentioned above as well.

None of this is particularly hard to do. The biggest part of the conversion is the removal of the 80C85 and the addition of a socket.

Cheers, comments welcome.