Optional ROM Drive

Per the following, 4 of 6 tests were completed.

I need to work out now how to flash the AM29F040 (fitted to XT-FDC) from DOS.

-----------------------------------------------------------------------------------

TEST 1: ADDRESS TEST 1 oF 2

a) Created an 512 KB binary file, where:

* First 8 KB block filled with byte 00

* Second 8 KB block filled with byte 01

* Third 8 KB block filled with byte 02

...

* Last 8 KB block filled with byte 3F (63 decimal)

b) Using an EPROM programmer, flashed that file into an AM29F040 chip.

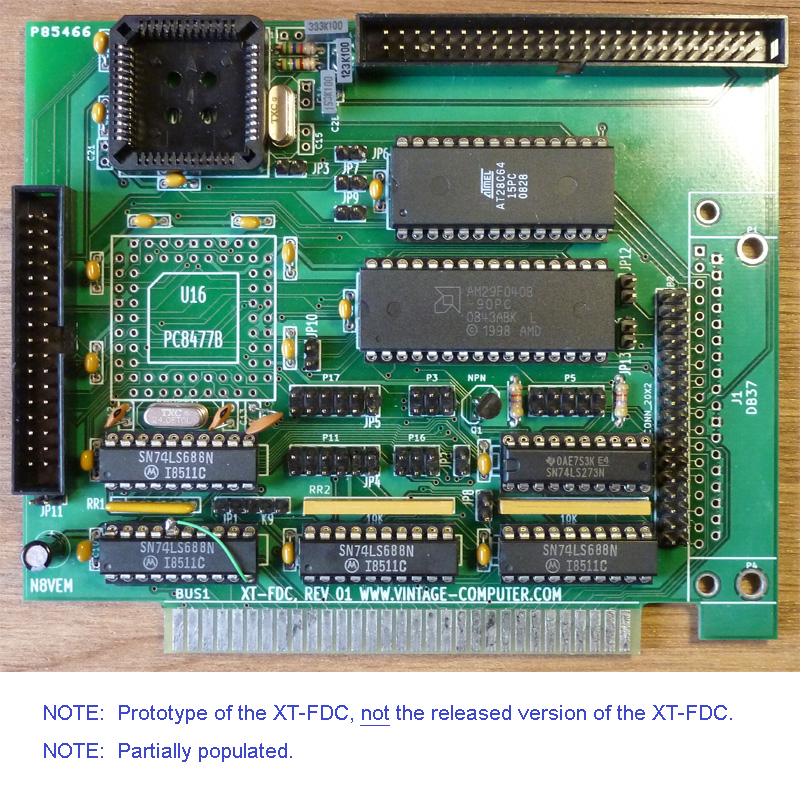

c) Fitted AM29F040 to XT-FDC.

d) Set P5 jumpers and JP7 for a ROM base address of C8000.

e) Verified via a custom DOS program that each 8 KB block ('selectable ROM') in the AM29F040 read as expected. The pseudo code was:

for each of the 63 'ROMs'

{

select the 8KB ROM .............. (comment: via an appropriate write to port 3F6h )

read entire 8KB ROM contents

report error if any byte read not the same as the ROM # (e.g. ROM #4 [logical] expected to contain bytes of 04 )

}

f) Using an EPROM programmer, changed one byte in the AM29F040.

g) Verified that my code detected that byte (i.e. in order to partially check my program's integrity).

-----------------------------------------------------------------------------------

TEST 2: READ DATA TEST

a) Using an EPROM programmer, modified first 18 bytes of AM29F040 to be:

00 / FF

01 / 02 / 04 / 08 / 10 / 20 / 40 / 80 (walking one)

7F / BF / DF / EF / F7 / FB / FD / FE (walking zero)

b) Fitted AM29F040 to XT-FDC.

c) Via DEBUG, verified that the first 18 bytes were as expected.

-----------------------------------------------------------------------------------

TEST 3: ADDRESS TEST 2 oF 2 (BASE ADDRESS OF 'SELECTABLE' 8KB ROM)

One of the things verified by test #1 was the generation of /CE on the AM29F040.

But it was done only using one possible base address, as selected by jumpers on P5 and by JP7.

Checked the card at various addresses, verifying that:

* ROM appeared at the selected address; and

* ROM did not also appear elsewhere.

Addresses checked: AA000/C8000/CA000/CC000/CE000/D0000/D2000/E0000

-----------------------------------------------------------------------------------

TEST 4: ROM ENABLE TEST (JP8)

Verified that removing JP8 resulted in the ROM no longer being 'seen'.

-----------------------------------------------------------------------------------

TEST 5: FLASH TEST

<pending>

-----------------------------------------------------------------------------------

TEST 6: WRITE ENABLE TEST (JP9)

<pending>

-----------------------------------------------------------------------------------