per

Veteran Member

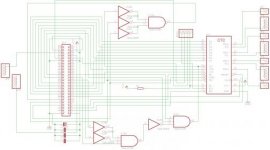

I'm fed up with one of my Z80 computer not having a VSync interrupt, or no indication on what goes on in the graphics hardware at all. Because of this, I decided to design a VSync interrupt expansion for it.

This device is pretty simple. It's designed for Interrupt Mode 2. You write the interrupt vector number with bit 7 set to an I/O port, and the device will then hopefully properly interrupt the Z80 CPU. Clearing bit 7 should disable the interrupting from the device. Interrupt is triggered if the /INT line is high when VSync triggers. /INT is pulled high by a pull-up resistor on the motherboard, and typically only the CTC will bother with interrupting.

Now, I cannot find to much discussion on the timing and hardware protocols around the Z80 interrupts. From what I understand the circuit I've come up with should work, but I'm not 100% certain. I don't really want to start ordering PCB's before I am safe this should be OK.

The main thing I am thinking about is when VSync is over before the interrupt is acknowledged. I problably have to use the other flip-flop in the LS74 to sample the VSync to /M1, as aborting the interupt during the acknowledge would be a bad idea.

This device is pretty simple. It's designed for Interrupt Mode 2. You write the interrupt vector number with bit 7 set to an I/O port, and the device will then hopefully properly interrupt the Z80 CPU. Clearing bit 7 should disable the interrupting from the device. Interrupt is triggered if the /INT line is high when VSync triggers. /INT is pulled high by a pull-up resistor on the motherboard, and typically only the CTC will bother with interrupting.

Now, I cannot find to much discussion on the timing and hardware protocols around the Z80 interrupts. From what I understand the circuit I've come up with should work, but I'm not 100% certain. I don't really want to start ordering PCB's before I am safe this should be OK.

The main thing I am thinking about is when VSync is over before the interrupt is acknowledged. I problably have to use the other flip-flop in the LS74 to sample the VSync to /M1, as aborting the interupt during the acknowledge would be a bad idea.