In the 1990s years I have designed a few small ZX81 and ZX97 based computers. In those days I had some collaboration with Wilf Rigter who made his own version of a ZX81 with some enhancements. I used some of his ideas in my ZX81 Issue 4 project at the time.

Since then I have done some larger projects and got into using CPLDs to be able to integrate a lot of logic and help scale down PCB design sizes. Also a CPLD has many advantages such as doing a lot of development on the circuits without actually needing to rewire a lot of things on the prototype.

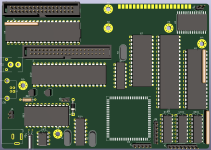

Last weekend I did a small experiment to wire a ATF1508AS onto my ZX81 Issue 4 PCB, and removing most ICs from the board, except the clock generator gate IC, CPU, RAM and ROM. After some revising and testing I found a reasonable equivalent CPLD design of the ZX81 ULA. Not 100% since the Sinclair ULA didn't need the /RFSH signal, for example, but that was also not my goal, I just wanted to realize a ZX81 in the CPLD and be left with as many spare CPLD pins as possible after completing the design. If we want, we also can figure out how not to need the /RFSH line to predict the refresh cycles, but that will only give us a single pin of the CPLD, which is not that important right now.

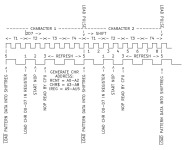

Having only the Dn lines on the CPLD pins needed some timing adjustments to be able to clock the character data before NOP is applied to the CPU, and then I needed to latch the D6 and D7 lines so they would be available for the "NOP" and "INVERT" decoding logic further along in the CPU cycle.

After finishing this first experiment, it looks attractive enough to make a computer with this idea, and I decided I will be making a PCB for this project which will include some other features in order to make the project more interesting. It's really not much work and I am doing this as a side project next to my larger designs. I am also looking into possibly running CP/M on the resulting computer, The challenge would be to merge CP/M bank switching with the ZX81 core computer, and somehow displaying the CP/M console. I am not sure if CP/M will be included but I am working on the schematic to test this idea if it would be feasible. I also want to look around which type of other interesting expansions I could include in this computer. The PCB is intended to fit inside the original ZX81 case. Later, I also will look into replacing the keyboard with something better. Maybe a RP2040 would be nice to include if some useful features could be found to make use of it.

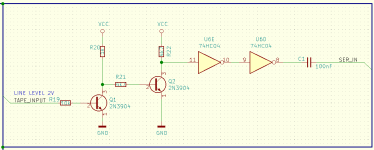

For the purpose of sharing these ideas for this very small experiment, I created a GitHub repository where you also can find my CPLD design which is able to functionally replace the ZX81 ULA. It's not fully done yet, but it is able to produce the display correctly and the keyboard is also functional. The only thing I plan to add to the ULA part of the design is to get some kind of back porch on the video output, I thought about tri stating the video output during the back porch period, and using some external circuit to take the composite signal to the back porch level during tri-state. Something like that.

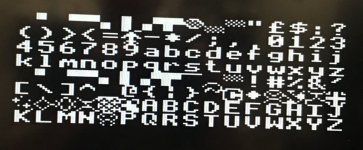

These days I am also reading Wilf Rigter's articles(I needed to search around for my old copies) and came across the CHR$128 modification which would allow for custom character sets to be realized for example for supporting games.

Does anyone know of some software which could test this modification out?

My first goal is integration, making the computer more useful, and also I want to be able to support as many games and programs as possible, so it would be useful to know which type of video enhancement related circuits would be good to include in the project in order to be able to run a larger number of games.

The ZX81-CPLD-V1 project can be found here.

I would appreciate any ideas and suggestions of expansions which could make this computer more functional.

I have some ideas and it depends on how useful, if it fits my project and how many components are needed.

If I can get CP/M to combine with the ZX81 functions, possibly a PPIDE harddisk would be nice and maybe a floppy drive.

And possibly a ZX81 program loader and saver could be realized using CP/M as the disk operating system.

CP/M is also able to read DOS diskettes which would be cool.

I know there are other solutions however having an elaborate OS would be valuable in this case in my opinion. CP/M would feel more retro.

Using bank switching, I imagine being able to switch back and forth between ZX81 mode and CP/M, and being able to run programs and data into the ZX81 computer.

I am looking at how many CPLD pins this would take with a minimal number of external components so I can get optimal use of the PCB space available in the tiny case.

It's really an advantage to be able to do all the decoding in the CPLD and this scales down the PCB area a lot.

Kind regards,

Rodney

Since then I have done some larger projects and got into using CPLDs to be able to integrate a lot of logic and help scale down PCB design sizes. Also a CPLD has many advantages such as doing a lot of development on the circuits without actually needing to rewire a lot of things on the prototype.

Last weekend I did a small experiment to wire a ATF1508AS onto my ZX81 Issue 4 PCB, and removing most ICs from the board, except the clock generator gate IC, CPU, RAM and ROM. After some revising and testing I found a reasonable equivalent CPLD design of the ZX81 ULA. Not 100% since the Sinclair ULA didn't need the /RFSH signal, for example, but that was also not my goal, I just wanted to realize a ZX81 in the CPLD and be left with as many spare CPLD pins as possible after completing the design. If we want, we also can figure out how not to need the /RFSH line to predict the refresh cycles, but that will only give us a single pin of the CPLD, which is not that important right now.

Having only the Dn lines on the CPLD pins needed some timing adjustments to be able to clock the character data before NOP is applied to the CPU, and then I needed to latch the D6 and D7 lines so they would be available for the "NOP" and "INVERT" decoding logic further along in the CPU cycle.

After finishing this first experiment, it looks attractive enough to make a computer with this idea, and I decided I will be making a PCB for this project which will include some other features in order to make the project more interesting. It's really not much work and I am doing this as a side project next to my larger designs. I am also looking into possibly running CP/M on the resulting computer, The challenge would be to merge CP/M bank switching with the ZX81 core computer, and somehow displaying the CP/M console. I am not sure if CP/M will be included but I am working on the schematic to test this idea if it would be feasible. I also want to look around which type of other interesting expansions I could include in this computer. The PCB is intended to fit inside the original ZX81 case. Later, I also will look into replacing the keyboard with something better. Maybe a RP2040 would be nice to include if some useful features could be found to make use of it.

For the purpose of sharing these ideas for this very small experiment, I created a GitHub repository where you also can find my CPLD design which is able to functionally replace the ZX81 ULA. It's not fully done yet, but it is able to produce the display correctly and the keyboard is also functional. The only thing I plan to add to the ULA part of the design is to get some kind of back porch on the video output, I thought about tri stating the video output during the back porch period, and using some external circuit to take the composite signal to the back porch level during tri-state. Something like that.

These days I am also reading Wilf Rigter's articles(I needed to search around for my old copies) and came across the CHR$128 modification which would allow for custom character sets to be realized for example for supporting games.

Does anyone know of some software which could test this modification out?

My first goal is integration, making the computer more useful, and also I want to be able to support as many games and programs as possible, so it would be useful to know which type of video enhancement related circuits would be good to include in the project in order to be able to run a larger number of games.

The ZX81-CPLD-V1 project can be found here.

I would appreciate any ideas and suggestions of expansions which could make this computer more functional.

I have some ideas and it depends on how useful, if it fits my project and how many components are needed.

If I can get CP/M to combine with the ZX81 functions, possibly a PPIDE harddisk would be nice and maybe a floppy drive.

And possibly a ZX81 program loader and saver could be realized using CP/M as the disk operating system.

CP/M is also able to read DOS diskettes which would be cool.

I know there are other solutions however having an elaborate OS would be valuable in this case in my opinion. CP/M would feel more retro.

Using bank switching, I imagine being able to switch back and forth between ZX81 mode and CP/M, and being able to run programs and data into the ZX81 computer.

I am looking at how many CPLD pins this would take with a minimal number of external components so I can get optimal use of the PCB space available in the tiny case.

It's really an advantage to be able to do all the decoding in the CPLD and this scales down the PCB area a lot.

Kind regards,

Rodney