Hi mogwaay,

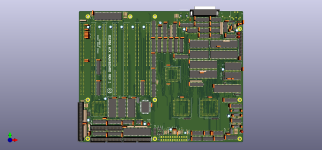

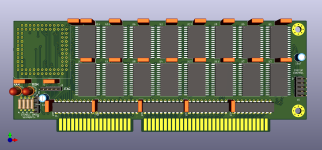

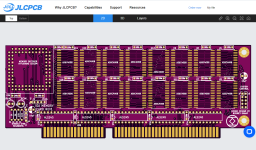

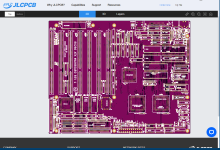

It's really great to hear from you here! I am always glad to talk with someone who has the same deeper interest in these historical vintage computers, which is also my reason for being here. Sharing ideas and inspiring eachother is what it's all about for me. I appreciate the compliments, thanks for that. I always feel I can do it even better in my designs because I will be paying the factory for making the boards, I always try to get the best result out of this service so it's hard to stop reworking the layout but I must force myself. My time should be limited because at the same time I want two things to happen, to have a result which feels right and I also need to drive this project to an actual result. For the mainboard I did get to the point where I am happy with the result. I am doing a lot of design verification work at the moment, trying to make as sure as possible before hand that the project has the best chance to function correctly, it is a very complex project.

I think I found your project at GitHub, it looks really interesting and I can see what your vision has been to create a kind of "home computer" style with only the things it needs and it looks like you did a nice job to realize it! I do love the idea and I also have some plans to revisit certain computers in a different form. I still want to do a "pizza box" format computer design and I plan to redesign the Amstrad PPC640D to replace the whole PCB inside mine with a single one. I am not sure if I will be using their chipsets on the new PCBs, or to possibly replace these with something else.

Next to the projects you have seen so far, I am also working occasionally on another 8088/V20 design with my daughter based on the 5150, specifically because it supports tape I/O which I want to play around with. In fact, looking back I am thinking I could have done this in the first place with my XT originally. At the time I was not sure about the differences of design between the 5150 and 5160 because I had not worked with the XT and PC schematics as much yet, so at the time I chose the 5160 because it was newer and could be possibly better. As I now have much more insight into the PC and XT logic, I could just as well have chosen the 5150 as a basis for the project. Fundamentally only the interrupt controller is wired and programmed differently in the 5150, and the IO space in the X-bus is more limited which can be changed of course. Maybe I will make a layout with footprints for both methods of programming and connecting the 8259 in case I need that later.

With a few small tweaks I believe it doesn't pose any compromises to go with the 5150 circuits in certain areas, while gaining the added advantage of the tape capability preserved. I want to experiment a lot with tape I/O in DOS as well. Like creating a file from a tape, or creating a tape from a file directly in DOS. Also I want to do advanced tape I/O monitoring by sound and LED indicators just to enjoy that retro experience of using a tape more. I have seen a Chinese ebay seller who is offering a lot of traditional analog tape circuit ICs, maybe new old stock, which may even make it possible to do some custom work on a tape drive, though I am not an analog expert, but I can get more experience and study existing tape drives of course. This project of a 5150 based mainboard is in the making and I will publish it later. It will also feature a RTC and some other enhancements. I bought a IBM 5150 "tank" case and power supply shell which I will design the PCBs for, just for a retro look and feel, and I will also do a redesign and create a 6845 based video card to be able to connect this setup with a CRT. More about this project later when it's done. That mainboard will also be ATX powered using a good ATX power supply transplanted into the original IBM PC power supply housing. At the same time this mainboard will be very integrated and feature "only" 5 expansion slots to match the 5150 case which is of course more than enough especially on an integrated mainboard.

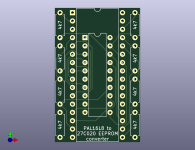

Thanks for your suggestions about the alternative programmer and software method, that is really helpful info and I was not aware of this. I will look into it later as a possible alternative. If I can cut some costs in a good way, I am also in favor of that. This project has already cost me a lot, especially loss of sleep working at night on the project so many times.

I will probably order the programmer that you mentioned as well now that I know this alternative exists. The one at Mouser is expensive, you are right, it lists as 93,59 euro in the Mouser shopping cart so it will cost me. Right now I just don't want to risk anything which could end up delaying the project unnecessarily for any reason. When I have a safe and good method to get the CPLDs working already, I can also do more testing later to compare if other methods also work just as well as the official one. I will share my CPLD experiences here and I will also read and research the thread from your link later, I will keep this in mind so thanks for that mogwaay!