Simplethings

Member

I have been doing some pondering over the schematic for the PS/2 Model 30/286. It's about the same thing as my model 25. I have noticed a few interesting things:

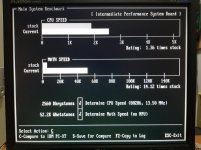

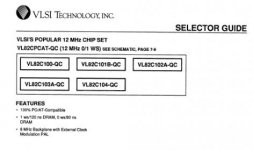

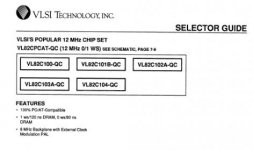

The chipset is a VLSI VL82CPCAT-QC and is capable of 12Mhz operation and zero wait states with 80nS RAM. :

The PS/2 Model 25/286 and model 30/286 both operate at 10Mhz with 1WS.

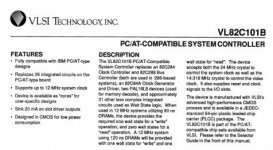

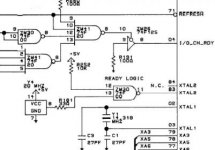

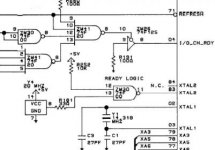

The VL82C101B System controller in these systems is what takes the 20Mhz Osc and splits it to 10Mhz (the speed our PS/2's run at)

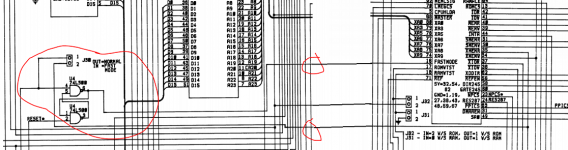

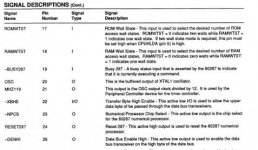

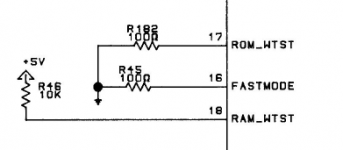

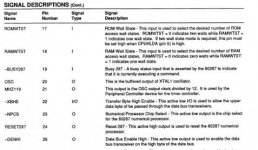

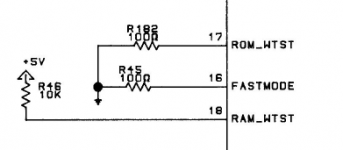

The RAM Wait state is enabled by pin 18 on the system controller:

On our PS2 machines pin 18 is hardwired to 5V, thus wait state is always on. FASTMODE is also always off. I'm not 100% How these work, but the datasheet for the chipset says it can run zero wait state at 12Mhz (our ps/2's are 10Mhz) with 80nS RAM. The stock PS2 ram is slow and can't run at that speed, but my computer is expanded to 4Mb with 80nS SIMMS.

I'm considering a few experiments, but I really don't want to destroy my PS/2. Has anyone attempted to travel this path before?

I'd like to try a few things. I have access to micro / mini level component repair and modification.

1) I'd like to switch the system controller osc from 20Mhz to 24Mhz and see if my PS/2 can run at 12Mhz. I'll probably buy the original style CPU at 12Mhz (they seem to be cheap and plentiful)

2) I'd like to make a jumper or switch of the wait state and fast mode setting.

If anyone is wondering "Why" it's kind of a pet project. I love the form factor, but the PS/2 model 25/286 is marginally faster than my 8086 with an NEC V30. With real VGA graphics, my ISA soundblaster 16, and 4MB of RAM I feel like this system is lacking just a touch of "oomph" in the processing department.

I don't want to post links so I don't get auto banned but I found the PS/2 model 30/286 schematic on google and the VLSI chipset info in a PDF document called VTI computer products 1989.

The chipset is a VLSI VL82CPCAT-QC and is capable of 12Mhz operation and zero wait states with 80nS RAM. :

The PS/2 Model 25/286 and model 30/286 both operate at 10Mhz with 1WS.

The VL82C101B System controller in these systems is what takes the 20Mhz Osc and splits it to 10Mhz (the speed our PS/2's run at)

The RAM Wait state is enabled by pin 18 on the system controller:

On our PS2 machines pin 18 is hardwired to 5V, thus wait state is always on. FASTMODE is also always off. I'm not 100% How these work, but the datasheet for the chipset says it can run zero wait state at 12Mhz (our ps/2's are 10Mhz) with 80nS RAM. The stock PS2 ram is slow and can't run at that speed, but my computer is expanded to 4Mb with 80nS SIMMS.

I'm considering a few experiments, but I really don't want to destroy my PS/2. Has anyone attempted to travel this path before?

I'd like to try a few things. I have access to micro / mini level component repair and modification.

1) I'd like to switch the system controller osc from 20Mhz to 24Mhz and see if my PS/2 can run at 12Mhz. I'll probably buy the original style CPU at 12Mhz (they seem to be cheap and plentiful)

2) I'd like to make a jumper or switch of the wait state and fast mode setting.

If anyone is wondering "Why" it's kind of a pet project. I love the form factor, but the PS/2 model 25/286 is marginally faster than my 8086 with an NEC V30. With real VGA graphics, my ISA soundblaster 16, and 4MB of RAM I feel like this system is lacking just a touch of "oomph" in the processing department.

I don't want to post links so I don't get auto banned but I found the PS/2 model 30/286 schematic on google and the VLSI chipset info in a PDF document called VTI computer products 1989.