dabone

Veteran Member

I've got a 2001N board someone sent me to take a look at. It's a 320350 board, no crtc.

It was missing the Character Rom and a 6520.

I've burned a 28c16 for the Character Rom and put in a good 6520.

(EEPROM works fine in my 2001N board)

I found that the crystal was dead and swapped in one I grabbed off an old pc board (16mhz.)

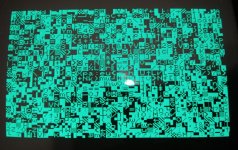

That brought the video back up. But it's just garbled, with a few characters kinda sparkling/changing.

I tested the 6502, 6522 and 6520 on my working 2001n. They all let my machine boot fine.

I also checked the roms (Basic 2) on my 2001n and the Kernal and one of the basic roms are dead.

I installed a Romulator, and went ahead and replaced the single wipe cpu socket with a dual wipe.

Reset circuit seems to be working correctly, held low for a short while, then high.

1Mhz Clock is present on the cpu.

I'm not getting any CAS on bank 0 or 1, so the Kernal isn't executing.

I've tried the following roms using the Romulator.

Pettester , Basic 2 Non-CRTC, Basic 4 Non-CRTC, Pet Low Ram Test, Pet RAM/ROM/VRAM Test.

When I enable the NOP generator on the Romulator, I'm getting pulsing on the cas lines. (Both ram banks)

Any suggestions on what to start checking next?

My available tools are Rigol 1054z scope, Logic Probe, lots of spare chips and sockets, multimeter, Another working pet.

It was missing the Character Rom and a 6520.

I've burned a 28c16 for the Character Rom and put in a good 6520.

(EEPROM works fine in my 2001N board)

I found that the crystal was dead and swapped in one I grabbed off an old pc board (16mhz.)

That brought the video back up. But it's just garbled, with a few characters kinda sparkling/changing.

I tested the 6502, 6522 and 6520 on my working 2001n. They all let my machine boot fine.

I also checked the roms (Basic 2) on my 2001n and the Kernal and one of the basic roms are dead.

I installed a Romulator, and went ahead and replaced the single wipe cpu socket with a dual wipe.

Reset circuit seems to be working correctly, held low for a short while, then high.

1Mhz Clock is present on the cpu.

I'm not getting any CAS on bank 0 or 1, so the Kernal isn't executing.

I've tried the following roms using the Romulator.

Pettester , Basic 2 Non-CRTC, Basic 4 Non-CRTC, Pet Low Ram Test, Pet RAM/ROM/VRAM Test.

When I enable the NOP generator on the Romulator, I'm getting pulsing on the cas lines. (Both ram banks)

Any suggestions on what to start checking next?

My available tools are Rigol 1054z scope, Logic Probe, lots of spare chips and sockets, multimeter, Another working pet.