Marty

Veteran Member

Hi All;

Dave, Thanks for the Responses..

""Can I ask you to double-check the work you have done today please. ""

Yes.. I have a feeling that, on the first four bits, it had two wires to each MBxx pin, and so It was easy to find the one going to the 7489's, which I switched..

But, on the Last eight bits, there was only One wire, and I switched it, But the other wire may have been on the 7489's instead of the 74175's and it got switched as well, unknowingly..

So I will check these connections as well..

"" Your CLL CML will "set" the LINK register. ""

I know this, This was my Intent..

"" The DCA will clear AC after it has finished. ""

This I didn't Realize.. My Bad..

"" A bit more about the TAD instruction (I think I can see where things are going wrong).

The TAD instruction (during the EXECUTE phase) uses the value in MB (from the FETCH phase) to add to the AC and store the result in AC during CP0. You can see this on schematic LD15 at the logic leading up to G15 input pin 3. The AND and TAD instructions gate AC(L) during CP0.

On schematic LD15, MB(L) is gated at F5. So the FETCH state machine should be cycling F0, F1, F2, F3 (this is the same as before) but then F4 (not A4) followed by F5 and then terminated by A6.

Interestingly (with your single step of my C:=A+B program) I am seeing the COMPLEMENT of the memory location stored in MB!

The output from MB should still drive the front panel lamps and go to the MUX that feeds one input of the ALU. MB should ***ONLY*** be inverted for feeding the data inputs to the 7489 RAMs (and NOT for anything else). ""

I will Check them all..

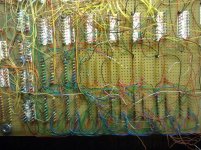

I figured Out the Problem with the LED Display, They were wired to the 7489's, and Not to the 74175's..

So, when I switched the 7489's to /MB the Display showed the Wrong Value, because it was tied to /MB and Not MB..

The MUX on bit '0' is correct along with the 74133 bit '0'..

The 74133 has been checked out, it is wired correctly..

The First four of the MUXes have been checked and are wired Correctly..

The First four of the Led Drivers were wired to the 7489's and are being Fixed..

The Middle four of the Led Drivers are wired to the 7489's and are being fixed..

The Middle four of the Muxes are wired Wrong, and have been fixed and checked..

The Last four of the Led Drivers are wired to the 7489's and are being fixed..

The Last four of the Muxes are wired Wrong, and have been fixed and checked..

With What All I am finding Wired Wrong, I am surprised that it Ran at all..

THANK YOU Marty

Dave, Thanks for the Responses..

""Can I ask you to double-check the work you have done today please. ""

Yes.. I have a feeling that, on the first four bits, it had two wires to each MBxx pin, and so It was easy to find the one going to the 7489's, which I switched..

But, on the Last eight bits, there was only One wire, and I switched it, But the other wire may have been on the 7489's instead of the 74175's and it got switched as well, unknowingly..

So I will check these connections as well..

"" Your CLL CML will "set" the LINK register. ""

I know this, This was my Intent..

"" The DCA will clear AC after it has finished. ""

This I didn't Realize.. My Bad..

"" A bit more about the TAD instruction (I think I can see where things are going wrong).

The TAD instruction (during the EXECUTE phase) uses the value in MB (from the FETCH phase) to add to the AC and store the result in AC during CP0. You can see this on schematic LD15 at the logic leading up to G15 input pin 3. The AND and TAD instructions gate AC(L) during CP0.

On schematic LD15, MB(L) is gated at F5. So the FETCH state machine should be cycling F0, F1, F2, F3 (this is the same as before) but then F4 (not A4) followed by F5 and then terminated by A6.

Interestingly (with your single step of my C:=A+B program) I am seeing the COMPLEMENT of the memory location stored in MB!

The output from MB should still drive the front panel lamps and go to the MUX that feeds one input of the ALU. MB should ***ONLY*** be inverted for feeding the data inputs to the 7489 RAMs (and NOT for anything else). ""

I will Check them all..

I figured Out the Problem with the LED Display, They were wired to the 7489's, and Not to the 74175's..

So, when I switched the 7489's to /MB the Display showed the Wrong Value, because it was tied to /MB and Not MB..

The MUX on bit '0' is correct along with the 74133 bit '0'..

The 74133 has been checked out, it is wired correctly..

The First four of the MUXes have been checked and are wired Correctly..

The First four of the Led Drivers were wired to the 7489's and are being Fixed..

The Middle four of the Led Drivers are wired to the 7489's and are being fixed..

The Middle four of the Muxes are wired Wrong, and have been fixed and checked..

The Last four of the Led Drivers are wired to the 7489's and are being fixed..

The Last four of the Muxes are wired Wrong, and have been fixed and checked..

With What All I am finding Wired Wrong, I am surprised that it Ran at all..

THANK YOU Marty

Last edited: