Hi All;

DDS, If I remember correctly,, "" I have no idea at this point whether the author's design needs the skew "" I read that if there is a problem with skew, that a different part could be put in.. Also, remember that in His design, the the Gates for Clock.Lo had two parallel gates for Loading.. And the Clock.Hi had four parallel gates to accommodate all of the Loads that it needed to drive..

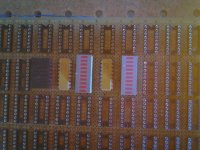

I have on my design, put the clock on the same Ic.. And I did the same type of thing on the Cpn's, I used two IC's just for the CPn's, so that I could put in anything I wanted, whether plain 7400 or LS, S, F.. And it would affect only those signals..

THANK YOU Marty